5 CPU页机制

IA-32 cpu支持分页机制,分页功能是可选功能。

5.1 三种分页模型

IA-32 目前支持三种分页模型

如果CR0寄存器的PG位=0,那么不启用分页功能。

如果要启用分页模式,CR0.PE 必须等于1

32位页模式

CR0.PG=1 , CR4.PAE=0

PAE页模式

CR0.PG=1,CR4.PAE=1,IA-32_EFER.LME=0

IA-32E页模式

CR0.PG=1,CR4.PAE=1,IA-32_EFER.LME=0

64位CPU使用

5.2 分页逻辑

各种模式下的分页功能基于集中分层页结构(hierarchical paging structures)实现。

每种页结构的大小是4KB,其中包含一系列的逻辑记录。

32 bit 页模式:每条记录大小4 byte,所以总共可以包含1024条记录

PAE页模式,IA-32e:每条记录8 byte,所以总共包含512条记录

每条页结构中的记录包含了一个物理地址,它指向另外一个页结构或者映射一个具体的内存页(page frame)。

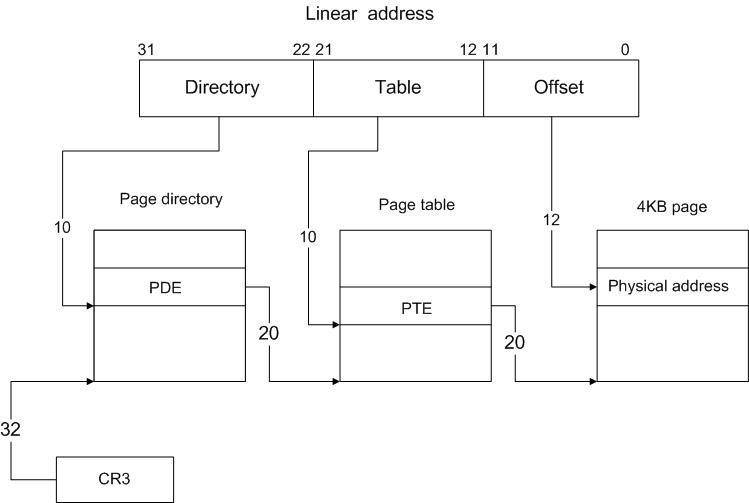

IA-32最多支持4层页结构逻辑,第一个页结构的地址通常保存在CR3中,第二个页结构由第一个页结构索引得出。因此,如果采用2级结构,32 bit的线性地址,从逻辑上可以拆成3部分 31:22 表示第一个页结构的索引,21:12 表示第二个页结构的索引,11:0 表示页内的偏移量。

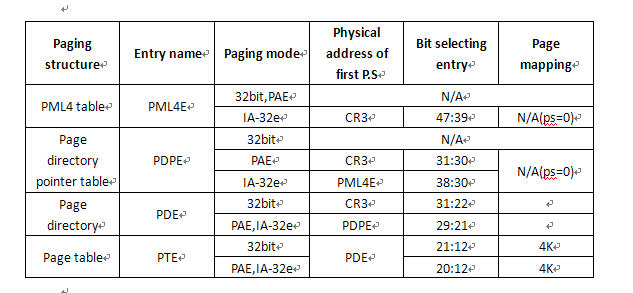

关于各种模式下的页结构名称以及页结构中的记录名称可以参考下表:

由该表可以归纳出

32bit 模式:用了2级数据结构PD----PT

PAE 模式:用了3级数据结构 PDPT-PD-PT

IA-32e 模式:用了 4级 数据结构: PML4T ----PDPT----PD----PT

第一级页结构都是由CR3保存其地址。

5.2.1 32 bit页模式

5.2.2 PAE页模式

暂时用不到,用到的时候再研究

5.2.3 IA-32e 页模式

暂时用不到,用到的时候再研究

6.逻辑地址转换到物理地址

在页功能没打开的时候,逻辑地址通过段逻辑转换到线性地址,直接映射到物理地址。

在页功能打开的时候,线性地址经过页逻辑转换到物理地址。