-

-

[翻译]Intel手册-VT部分 第28章 VM EXITS

-

发表于: 2024-4-22 00:22 9923

-

VM Exits是为了响应 VMX non-root operation中的某些指令和事件而发生,如第 26.1 节到第 26.2 节所述。 VM退出执行以下操作:

VM Exits不会记录最后一个分支记录,不会生成分支跟踪消息,并且不会更新分支跟踪存储。

第 28.1 节阐明了 VM Exits开始之前架构状态的性质。第 28.2 节到第 28.6 节详细介绍了上述步骤。

第 32.15 节描述了系统管理中断(SMI)和系统管理模式(SMM)的双监视器处理。在这种处理下,到 SMM 的普通转换被 VM Exits到单独的 SMM 监视器所取代。称为 SMM VM Exits,这些是由 SMI 的到达或 VMX root operation中 VMCALL 的执行引起的。 SMM VM 出口与其他 VM 出口的不同之处详见第 32.15.2 节。

本节描述 VM Exits之前存在的体系结构状态,特别是由通常通过 IDT 传递的事件引起的 VM Exits。请注意以下事项:

以下要点详细说明了何时更新架构状态以响应 VM Exits:

如果事件直接导致 VM Exits,则它不会像没有导致 VM Exits时那样更新体系结构状态:

调试异常不会更新 DR6、DR7 或 IA32_DEBUGCTL。 (有关调试异常性质的信息保存在退出限定字段中。)

页面错误不会更新 CR2。 (导致页面错误的线性地址保存在退出限定字段中。)

NMI 会导致后续 NMI 被阻止,但仅限于 VM Exits完成之后。

外部中断不会确认中断控制器,并且中断保持挂起状态,除非“退出时确认中断”VM-exit 控制为 1。在这种情况下,中断控制器被确认并且中断不再挂起。

当任务切换导致 VM Exits时,DR7 中的标志 L0 – L3(位 0、位 2、位 4 和位 6)不会被清除。

如果任务切换导致 VM Exits,则任务切换不会修改以下任何内容: 旧任务状态段 (TSS);新的 TSS;旧的 TSS 描述符;新的 TSS 描述符; RFLAGS.NT1;或 TR 寄存器。

如果事件直接导致 VM Exits,则不会创建最后异常记录。

如果机器检查异常直接导致VM退出,这不会阻止机器检查MSR的更新。这些是由机器检查事件本身更新的,而不是由生成的机器检查异常更新的。

如果逻辑处理器处于非活动状态(参见第 25.4.2 节)并且不执行指令,则某些事件可能会被阻止,但其他事件可能会将逻辑处理器返回到活动状态。未阻止事件可能会导致 VM Exits。2 如果未阻止事件直接导致 VM Exits,则仅在 VM Exits完成后才会返回到活动状态。3 VM Exits会生成通常在活动状态处于活动状态时生成的任何特殊总线周期。从该活动状态进入。

MTF VM 出口(参见第 26.5.2 节和第 27.7.8 节)在 HLT 活动状态下不会被阻止。如果在 HLT 活动状态下发生 MTF VM Exits,则逻辑处理器仅在 VM Exits完成后才返回到活动状态。 MTF VM退出被阻塞在关闭状态和等待SIPI状态。

如果某个事件间接导致 VM Exits,则该事件会更新体系结构状态:

如果“虚拟 NMI”VM 执行控制为 1,则 VM entries注入 NMI,并且 NMI 的传递会导致嵌套异常、双重错误、任务切换、EPT 违规、EPT 配置错误、页面修改日志满事件或SPP 相关事件或导致 VM Exits的 APIC 访问、虚拟 NMI 阻止在 VM Exits开始之前生效。

如果 VM Exits是由于 IRET 执行期间遇到的故障、EPT 违规、EPT 错误配置、页面修改日志满事件或 SPP 相关事件导致的,并且“NMI 退出”VM 执行控制为 0,则任何阻塞在 VM Exits开始之前,由 NMI 清除。然而,之前被NMI阻止的状态可以记录在退出资格中或者VM-退出中断信息字段中;参见第 28.2.3 节。

假设 VM Exits是由 x87 FPU 浮点错误 (#MF) 直接引起的,或者是由以下任何事件引起的(如果该事件由于 x87 FPU 浮点错误而被解除阻止(并具有优先级): INIT信号、外部中断、NMI、SMI;或机器检查异常。在这些情况下,当 VM Exits开始时,STI 或 MOV SS 不会阻塞。

通常,当通过IDT传递事件时,可以进行最后分支记录。但是,如果此类事件导致 VM 在交付完成之前退出,则不会创建最后一个分支记录。

如果机器检查异常导致 VM Exits,则处理器状态是可疑的,并且可能导致可疑状态被保存到guest 状态区域。在恢复因机器检查异常导致 VM Exits的 guest 虚拟机之前,VM 监视器应查阅 IA32_MCG_STATUS MSR 中的 RIPV 和 EIPV 位。

以下VM退出被认为是在指令执行后发生:

由于调试陷阱(单步、I/O 断点和数据断点)导致 VM Exits。

VM 因调试异常(数据断点)而退出,该异常的识别因 MOV SS 的阻塞而延迟。

由于某些机器检查异常而导致虚拟机退出。

当“CR8加载退出”VM执行控制为0并且“使用TPR影子”VM执行控制为1时,由于执行MOV到CR8,类陷阱VM退出(参见第30.3节)。 (此类 VM Exits只能在 64 位模式下发生,因此只能在支持 Intel 64 架构的处理器上发生。)

当“使用 MSR 位图”VM 执行控制为 1 时,由于执行 WRMSR,类陷阱 VM Exits; ECX的取值范围为800H~8FFH;低MSR的写位图中ECX值对应的位为0; “虚拟化 x2APIC 模式”VM 执行控制为 1。请参见第 30.5 节。

由 APIC 写入仿真(参见第 30.4.3.2 节)引起的 VM Exits,该仿真是由 APIC 访问(作为指令执行的一部分)引起的。

对于这些VM退出,指令对架构状态的修改在VM退出发生之前完成。此类修改包括对逻辑处理器的可中断性状态的修改(参见表 25-3)。如果在指令执行之前已经被 MOV SS、POP SS 或 STI 阻塞,则该阻塞不再有效。

飞地模式下发生的 VM Exits会设置退出原因字段的位 27 和客户机中断状态字段的位 4。在传送此类 VM Exits之前,会发生异步 Enclave 退出 (AEX)(请参阅第 37 章“Enclave 退出事件”)。 AEX 修改架构状态(第 37.3 节)。特别是,处理器建立如下所示的架构状态:

VM Exits首先在 VM Exits信息字段中记录有关 VM Exits的性质和原因的信息。第 28.2.1 节到第 28.2.5 节详细介绍了这些字段的使用。

除了更新VM退出信息字段之外,还清除VM进入中断信息字段中的有效位(位31)。如果 IA32_VMX_MISC MSR(索引 485H)的位 5 被读取为 1(参见附录 A.6),则 IA32_EFER.LMA 的值将存储到“IA-32e 模式guest ”VM 输入控件中。

第 25.9.1 节定义了基本的 VM Exits信息字段。以下项目详细介绍了它们的用途。

退出原因。

该字段的位 15:0 包含基本退出原因。它加载了一个数字,指示 VM Exits的一般原因。附录 C 列出了所使用的数字及其含义。

如果“过早繁忙影子堆栈”VM Exits控制为 1 并且 VM Exits导致影子堆栈过早繁忙(请参阅第 26.4.3 节),则设置位 25。否则,该位被清除。

如果在总线锁定断言之后发生 VM Exits,同时“VMM 总线锁定检测”VM 执行控制为 1,则该字段的位 26 设置为 1。此类 VM Exits包括由于 1 设置而发生的 VM Exits。该控制以及在执行断言总线锁定的指令期间可能发生的其他控制。

如果逻辑处理器处于 enclave 模式时发生 VM Exits,则该字段的位 27 设置为 1

此类VM退出包括由中断、不可屏蔽中断、系统管理中断、INIT信号和飞地模式中发生的异常以及在飞地模式中发生的此类事件的传递期间遇到的异常引起的退出。

如果 VM entry所注入的事件的传递发生并且guest 中断状态字段指示飞地中断(该字段的位 4 为 1),则 VM 出口也会设置该位。

该字段的其余部分(位 31:28 和位 24:16)被清除为 0(某些 SMM VM 出口可能会设置其中一些位;请参阅第 32.15.2.3 节)。

退出资格。由于以下原因而导致虚拟机退出时,会保存此字段:调试异常;页面错误异常;初创企业 IPI (SIPI);执行 I/O 指令后立即到达的系统管理中断 (SMI);任务切换;投资; INVLPG; INVPCID; INVVPID; LGDT;激光损伤检测; LLDT;长期关系; SGDT; SIDT; SLDT; STR; VM清除; VMPTRLD; VMPTRST;虚拟机读取;虚拟机写入; VMXON; WBNVD; WBNOINVD; XRSTORS; X保存;控制寄存器访问; MOV 博士; I/O指令;等待;访问 APIC 访问页面(参见第 30.4 节); EPT 违规行为(参见第 29.3.3.2 节); EOI 虚拟化(参见第 30.1.4 节); APIC 写入仿真(参见第 30.4.3.3 节);页面修改日志已满(参见第 29.3.6 节); SPP 相关事件(参见第 29.3.4 节);和指令超时(参见第 26.2 节)。对于所有其他 VM 出口,该字段被清除。以下项目提供详细信息:

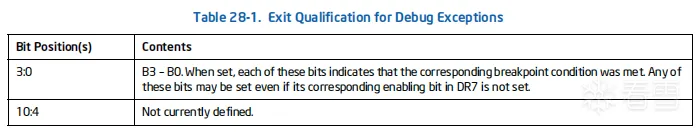

对于调试异常,退出限定包含有关调试异常的信息。这

信息的格式如表 28-1 所示。

笔记:

一般来说,该字段的格式与DR6的格式一致。然而,DR6 清零位 11 以指示检测到总线锁定,而该字段设置该位以指示该情况。

一般来说,该字段的格式与DR6的格式一致。然而,DR6 清除位 16 以指示与 RTM 相关的异常,而该字段设置该位以指示该情况。

对于页错误异常,退出限定包含导致页错误的线性地址。在支持 Intel 64 架构的处理器上,如果逻辑处理器在 VM Exits之前未处于 64 位模式,则清除位 63:32。

如果页错误异常发生在飞地模式下的指令执行期间(而不是在传送飞地模式的事件期间),则退出资格的位 11:0 被清除。

对于启动 IPI (SIPI),退出资格包含位 7:0 中的 SIPI 向量信息。退出资格的位 63:8 被清除为 0。

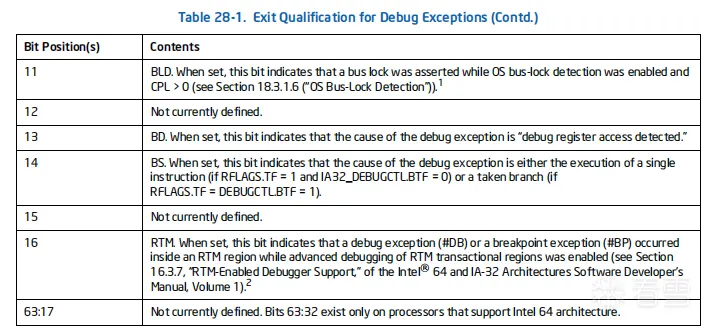

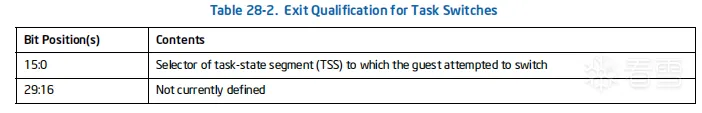

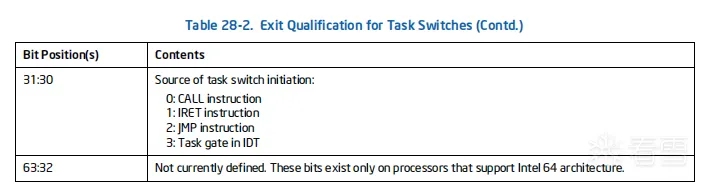

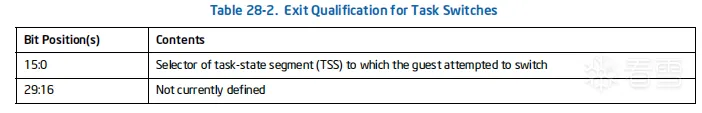

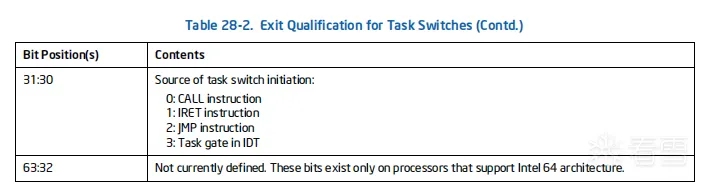

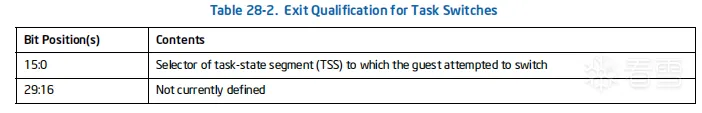

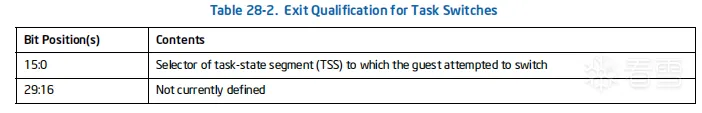

对于任务切换,退出限定包含有关任务切换的详细信息,编码如表 28-2 所示。

对于 INVLPG,退出限定包含指令的线性地址操作数。

在支持 Intel 64 架构的处理器上,如果逻辑处理器在 VM Exits之前未处于 64 位模式,则清除位 63:32。

如果 INVLPG 源操作数指定不可用的段,则退出限定中指定的线性地址将与 INVLPG 在未发生 VM Exits时使用的线性地址相匹配。该地址没有在体系结构上定义,并且可能是特定于实现的。

对于 INVEPT、INVPCID、INVVPID、LGDT、LIDT、LLDT、LTR、SGDT、SIDT、SLDT、STR、VMCLEAR、VMPTRLD、VMPTRST、VMREAD、VMWRITE、VMXON、XRSTORS 和 XSAVES,退出限定接收指令位移的值字段,如有必要,该字段将符号扩展为 64 位(在不支持 Intel 64 架构的处理器上为 32 位)。如果指令没有位移(例如,有寄存器操作数),则将零存储到退出限定中。

在支持 Intel 64 架构的处理器上,RIP 相对寻址(仅在 64 位模式下使用)是一个例外。此类寻址使指令使用的地址是位移字段与引用后续指令的 RIP 值之和。在这种情况下,退出资格加载位移场和适当的 RIP 值的总和。

在所有情况下,该字段超出指令地址大小的位都是未定义的。例如,假设 VM Exits指令信息字段(参见第 25.9.4 节和第 28.2.5 节)中的地址大小字段报告 n 位地址大小。那么指令位移的位 63: n(在不支持 Intel 64 架构的处理器上为位 31: n)未定义。

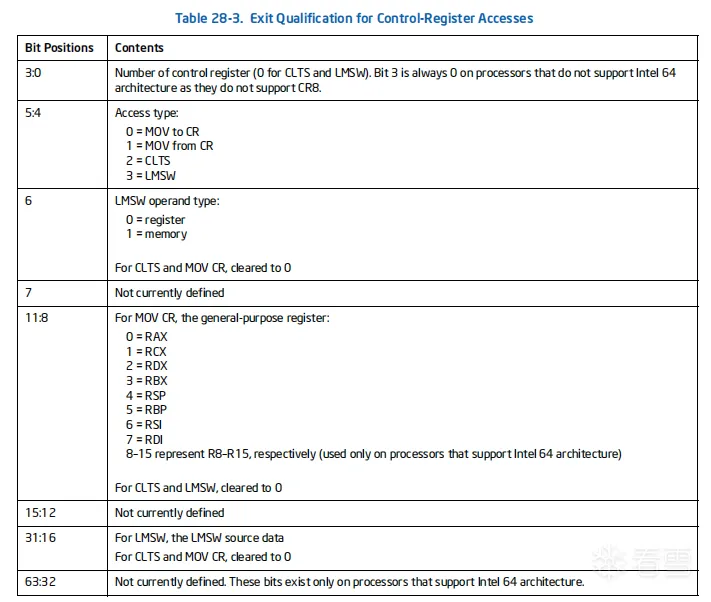

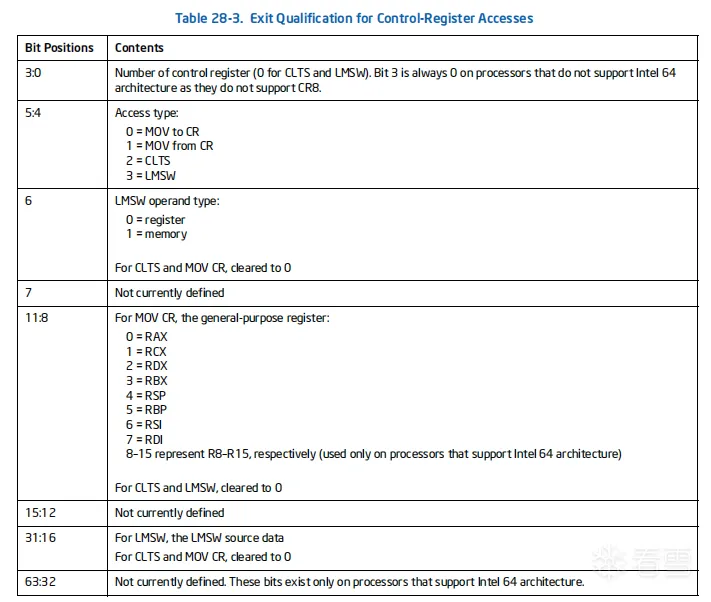

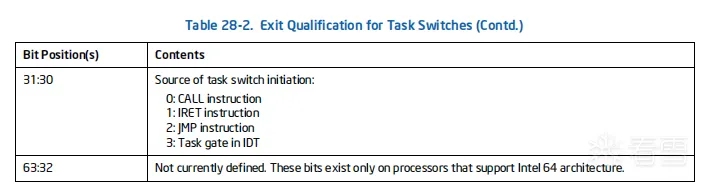

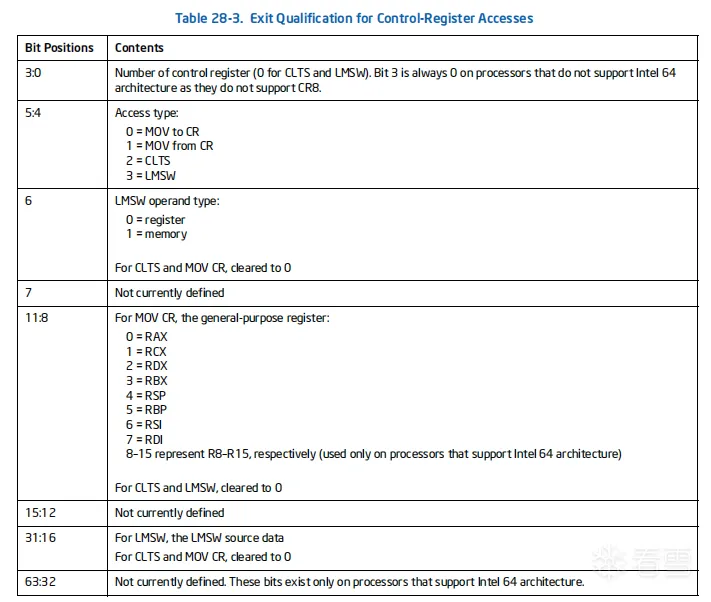

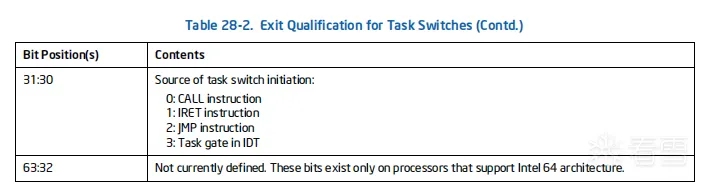

对于控制寄存器访问,退出限定包含有关访问的信息,其格式如表 28-3 所示。

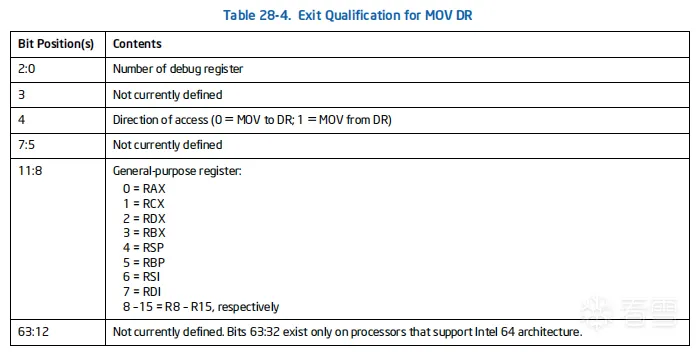

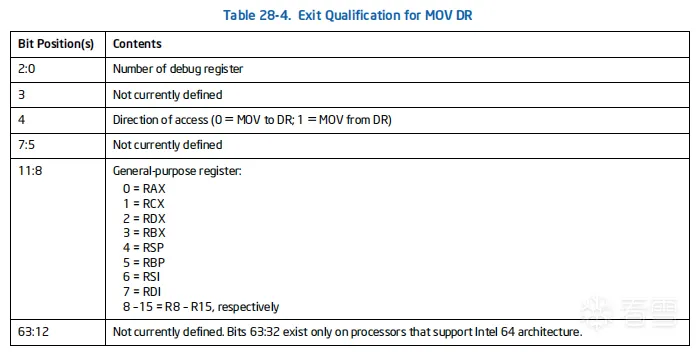

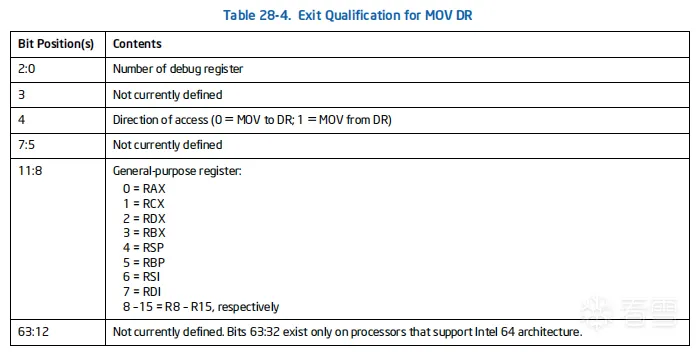

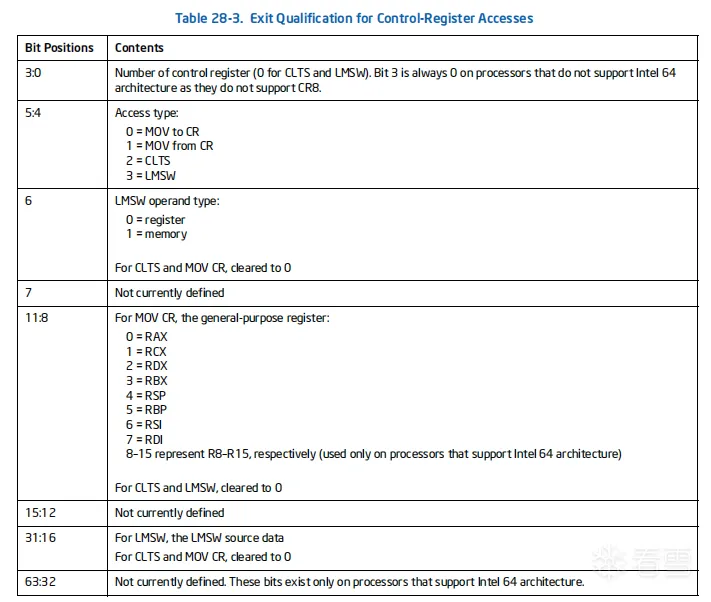

对于 MOV DR,退出限定包含有关指令的信息,其格式如表 28-4 所示。

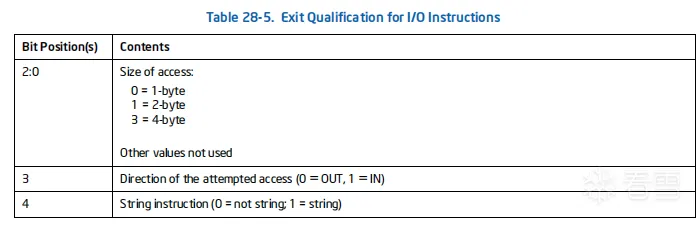

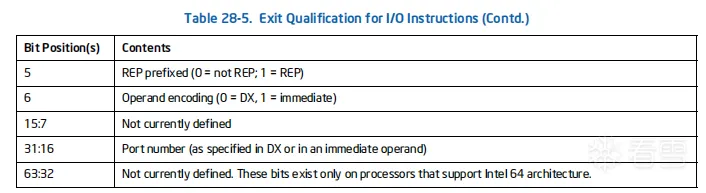

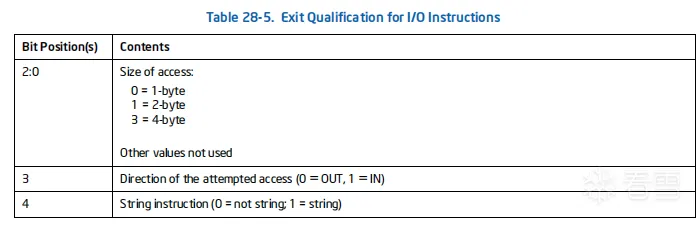

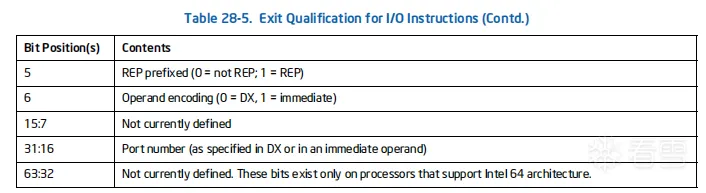

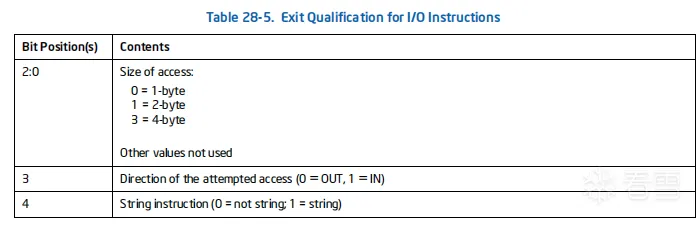

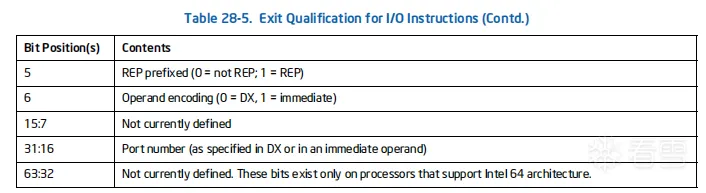

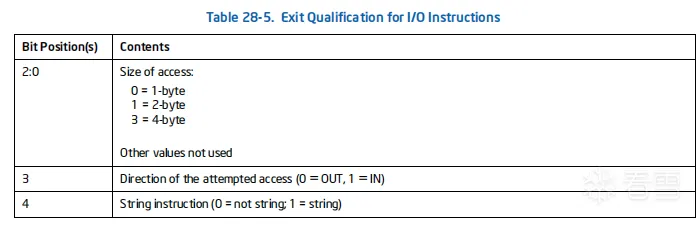

对于 I/O 指令,退出限定包含有关指令的信息,其格式如表 28-5 所示。

对于 MWAIT,退出限定包含一个值,该值指示是否进行地址范围监控

硬件已武装。退出资格设置为 0(如果地址范围监控硬件未配备)或 1(如果地址范围监控硬件配备)。

WBINVD 和 WBNOINVD 使用相同的基本退出原因(请参阅附录 C)。对于 WBINVD,退出资格为 0,而对于 WBNOINVD,退出资格为 1。

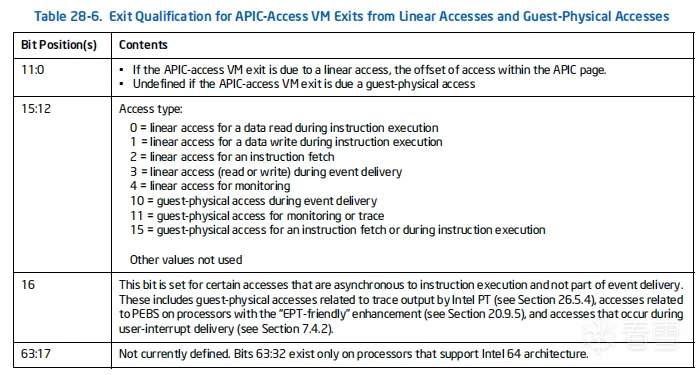

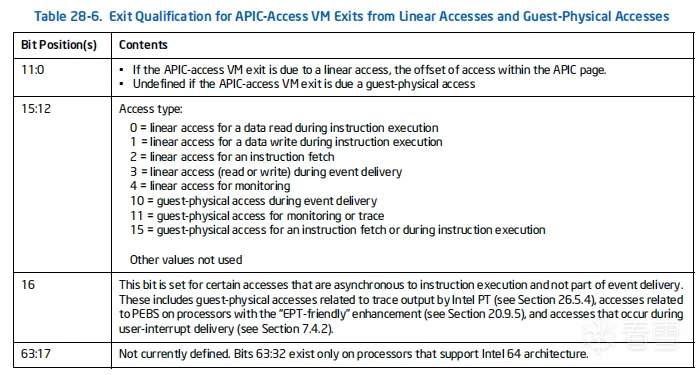

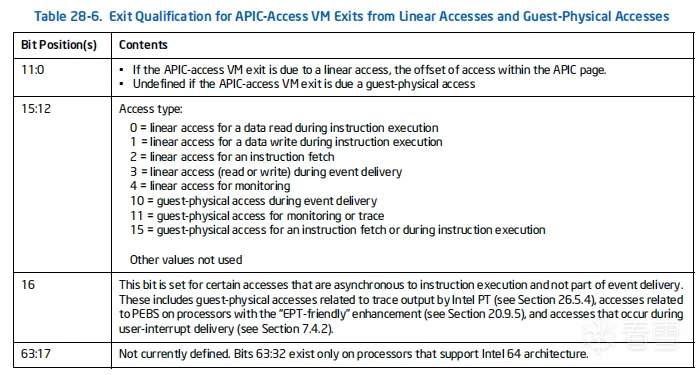

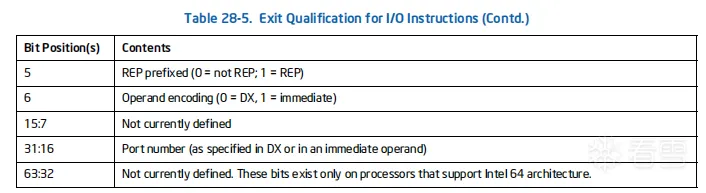

对于由于对 APIC 访问页面的线性访问或guest 物理访问而导致的 APIC 访问 VM Exits(请参阅第 30.4 节),退出限定包含有关访问的信息,并具有表 28-6 中给出的格式。

如果对 APIC 访问页的访问发生在飞地模式下的指令执行期间(而不是在飞地模式发生事件的传送期间),则退出资格的位 11:0 被清除。

这样的 VM Exits将退出限定的位 15:12 设置为 0000b(指令执行期间读取数据)或 0001b(指令执行期间数据写入)将位 12(区分数据读取和数据写入)设置为存储在页错误错误代码的位 1(W/R)中的访问导致了页错误,而不是 APIC 访问 VM Exits。这意味着以下内容:

对于由 CLFLUSH 和 CLFLUSHOPT 指令引起的 APIC 访问 VM Exits,访问类型是“指令执行期间读取数据”。

对于由ENTER指令引起的APIC访问VM退出,访问类型是“指令执行期间的数据写入”。

对于由MASKMOVQ指令或MASKMOVDQU指令引起的APIC访问VM退出,访问类型是“指令执行期间的数据写入”。

对于由 MONITOR 指令引起的 APIC 访问 VM Exits,访问类型是“指令执行期间读取数据”。

对于由于访问 DS 保存区(BTS 或 PEBS)中的线性地址直接导致的 APIC 访问 VM Exits,访问类型为“用于监视的线性访问”。

对于因访问 DS 保存区域(例如,访问分页结构以转换线性地址)而执行的guest 物理访问而导致的 APIC 访问 VM Exits,访问类型为“用于监视或监视的guest 物理访问”痕迹。”

对于当“Intel PT 使用guest 物理地址”VM 执行控制为 1 时由跟踪地址预转换 (TAPT) 导致的 APIC 访问 VM Exits,访问类型为“用于监视或跟踪的guest 物理访问”。

当且仅当它将退出资格的位 15:12 设置为 0011b(事件传递期间的线性访问)或 1010b(guest 物理事件交付期间的访问)。

有关这些指令和 APIC 访问 VM 出口的进一步讨论,请参见第 30.4.4 节。

对于因物理访问 APIC 访问页面而导致的 APIC 访问 VM Exits(请参阅第 30.4.6 节),退出资格未定义。

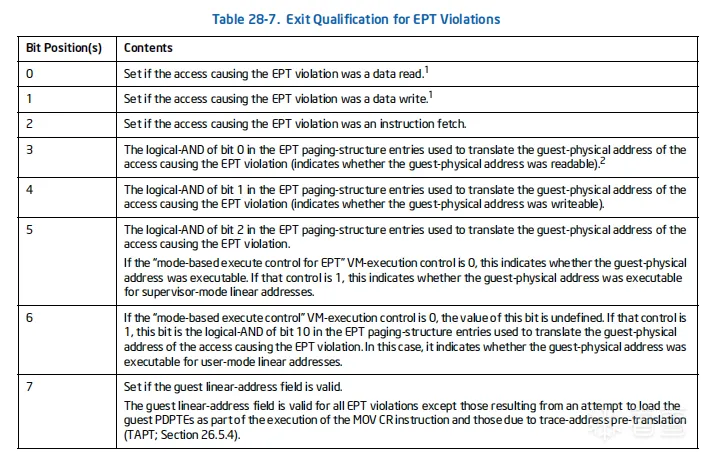

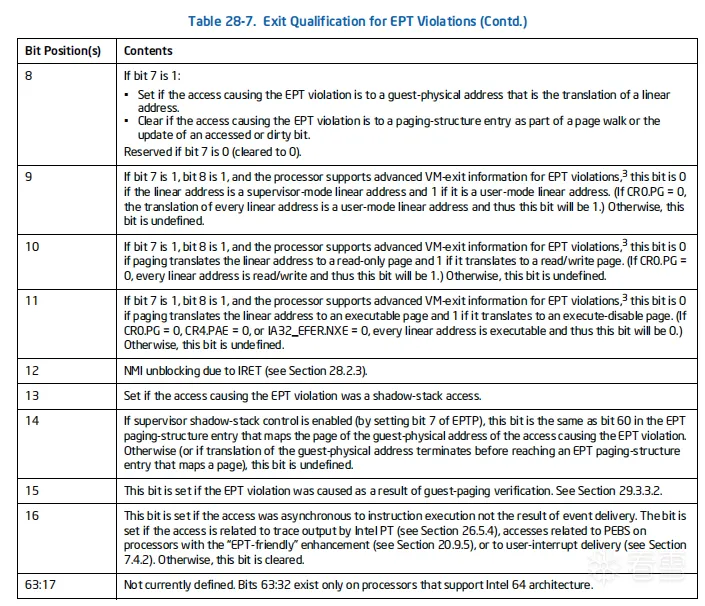

对于 EPT 违规,退出资格包含有关导致 EPT 违规的访问的信息,并具有表 28-7 中给出的格式。

如该表中所述,退出资格的格式和含义取决于“EPT 的基于模式的执行控制”VM 执行控制的设置以及处理器是否支持针对 EPT 违规的高级 VM Exits信息。

由于执行读取-修改-写入操作而发生的 EPT 违规设置位 1(数据写入)。是否也设置位 0(数据读取)是特定于实现的,并且对于给定的实现,对于不同类型的读取-修改-写入操作可能有所不同。

位 12 报告“NMI 由于 IRET 解锁”;参见第 28.2.3 节。

位 16 被设置用于与指令执行异步且不是事件传递的一部分的某些访问。其中包括 Intel PT 的跟踪地址预translation (TAPT)(请参阅第 26.5.4 节)、与具有“EPT 友好”增强功能的处理器上的 PEBS 相关的访问(请参阅第 20.9.5 节)以及作为用户一部分的访问- 中断传送(参见第 7.4.2 节)。

对于作为 EOI 虚拟化的一部分引起的 VM Exits(第 30.1.4 节),退出资格的位 7:0 设置为由 EOI 虚拟化消除的虚拟中断的向量。位 7 以上的位被清除。

对于 APIC 写入 VM Exits(第 30.4.3.3 节),退出限定的位 11:0 设置为导致 VM Exits的写访问的页偏移量。1 位 11 以上的位被清除。

对于由于页面修改日志满事件(第 29.3.6 节)而导致的 VM Exits,退出资格的位 12 报告“由于 IRET 导致 NMI 解锁”(请参阅第 28.2.3 节)。如果在 TAPT、EPT 友好的 PEBS 或用户中断传送期间发生 VM Exits,则设置位 16。退出资格的所有其他位均未定义。

对于由于 SPP 相关事件(第 29.3.4 节)而导致的 VM Exits,退出资格的位 11 指示事件类型:0 指示 SPP 配置错误,1 指示 SPP 未命中。退出资格的位 12 报告“NMI 由于 IRET 解锁”(参见第 28.2.3 节)。如果在 TAPT EPT 友好的 PEBS 或用户中断传送期间发生 VM Exits,则设置位 16。退出资格的所有其他位均未定义。

如果“PASID 转换”VM 执行控制,则为 ENQCMD 和 ENQCMDS 指令的执行执行 PASID 转换(请参见第 26.5.8 节)。 PASID 转换可能会失败,从而导致 VM Exits。这样的VM退出保存在以下项目中指定的退出资格:

对于由于指令超时而导致的 VM Exits(第 26.2 节),位 0 指示(如果设置)虚拟机的上下文无效并且不应恢复 VM。退出资格的位 12 报告“NMI 由于 IRET 解锁”(参见第 28.2.3 节)。退出资格的所有其他位均未定义。

笔记:

-

VM 由于设置退出资格的位 7 的 EPT 违规而退出(参见表 28-7;这些都是 EPT 违规,除了由于执行 MOV CR 指令时尝试加载 PDPTE 导致的违规以及由于 TAPT 导致的违规) 。线性地址可以转换为其访问导致EPT违规的客户物理地址。或者,线性地址的转换可以引用其访问导致EPT违规的分页结构条目。如果在 VM Exits之前逻辑处理器未处于 64 位模式,则清除位 63:32。

如果在飞地模式下执行指令期间发生 EPT 违规(而不是在传送飞地模式中发生的事件期间),则该字段的位 11:0 被清除。

VM 由于 SPP 相关事件而退出。

如果“过早繁忙的影子堆栈”VM Exits控制为 1,如果 VM Exits导致影子堆栈过早繁忙,则某些 VM Exits(除了上面提到的那些)会保存与 VM Exits相关的线性地址(请参见第 26.4 节) .3).由于以下原因,VM Exits也是如此:EPT 配置错误、页面修改日志已满事件和指令超时。 (由于指令超时而导致的 VM Exits设置了退出资格的位 0,表明 VM 上下文无效,不会保存有效的线性地址。)

对于所有其他 VM 出口,该字段未定义。

guest 实际地址。对于由于 EPT 违规、EPT 配置错误或 SPP 相关事件而导致的 VM Exits,此字段接收导致 EPT 违规或 EPT 配置错误的guest 物理地址。对于所有其他 VM 出口,该字段未定义。

如果在飞地模式下执行指令期间发生 EPT 违规或 EPT 错误配置(而不是在传送飞地模式事件期间),则该字段的位 11:0 被清除。

第 25.9.2 节定义了包含由于以下事件导致的 VM Exits信息的字段: 异常(包括由指令 INT1、INT3、INTO、BOUND、UD0、UD1 和 UD2 生成的异常);当“退出时确认中断”VM-exit 控制为 1 时发生的外部中断; 1 此类 VM Exits包括在尝试任务切换时发生的退出,该任务切换导致在由于导致 VM Exits的任务切换而生成 VM Exits之前导致异常。

以下各项详细说明了这些字段的使用:

VM退出中断信息(格式见表25-19)。以下项目详细说明了如何为由于这些事件而导致 VM Exits建立此字段:

对于异常,位 7:0 接收异常向量(最多 31)。对于 NMI,位 7:0 设置为 2。对于外部中断,位 7:0 接收向量

位 10:8 设置为 0(外部中断)、2(不可屏蔽中断)、3(硬件异常)、5(特权软件异常)或 6(软件异常)。硬件异常包括除以下情况之外的所有异常:

INT1指令产生的调试异常(#DB);这些是特权软件例外。 (其他调试异常被视为硬件异常,就像在 enclave 模式下执行 INT1 引起的异常一样。)

断点异常(#BP;由 INT3 生成)和溢出异常(#OF;由 INTO 生成);这些是软件例外情况。 (飞地模式下发生的 #BP 被视为硬件异常。)

超出 BOUND 范围的异常(#BR;由 BOUND 生成)和由 UD0、UD1 和 UD2 生成的无效操作码异常(#UD)是硬件异常。

如果 VM Exits是由硬件异常引起的,并且该异常会在堆栈上传递错误代码,则位 11 将设置为 1。如果逻辑处理器处于实地址模式 (CR0.PE=0) 时发生 VM Exits,则该位始终为 0。2 如果位 11 设置为 1,则错误代码置于 VM Exits中断错误代码中(见下文)

位 12 报告“NMI 由于 IRET 解锁”;参见第 28.2.3 节。如果VM退出是由于双重故障(中断类型为硬件异常,向量为8),则该位的值未定义。

位 30:13 始终设置为 0。

位 31 始终设置为 1。

对于其他 VM Exits(包括当“退出时确认中断”VM Exits控制为 0 时由于外部中断而导致的退出),该字段被标记为无效(通过清除位 31)并且该字段的其余部分未定义。

VM-退出中断错误代码

对于在 VM Exits中断信息字段中同时设置位 31(有效)和位 11(错误代码有效)的 VM Exits,该字段接收在事件导致 VM Exits时本应推送到堆栈上的错误代码通过 IDT 正常交付。 EXT 位在此字段中的设置与正常设置时完全相同。对于在传送双重故障期间发生的异常(如果 IDT 向量信息字段指示双重故障),EXT 位设置为 1,假设 (1) 异常会正常产生错误代码(如果没有发生) (2) 错误代码使用 EXT 位(不适用于页错误,页错误使用不同的格式)。

对于其他VM出口,该字段的值未定义。

在执行 IRET 指令期间,可能会由于以下原因发生 VM Exits:故障、EPT 违规、页面修改日志已满事件、SPP 相关事件或指令超时。

在不可屏蔽中断 (NMI) 被阻止时开始执行 IRET,即使发生故障或 VM Exits,也会解除对 NMI 的阻止;此类 VM Exits保存的状态将指示 NMI 未被阻止。

由于上述原因而退出的 VM 通过保存一个称为“由于 IRET 导致的 NMI 解锁”的位来向软件提供更多信息。如果 (1) “NMI 退出”VM 执行控制为 0 或“虚拟 NMI”VM 执行控制为 1,则定义该位; (2) VM出口未设置IDT向量信息字段中的有效位(参见第28.2.4节); (3)VM退出不是由于双重故障。在这些情况下,该位定义如下:

对于由于故障而导致的VM退出,由于IRET而导致的NMI解除阻塞被保存在VM退出中断信息字段的位12中(第28.2.2节)。对于由于 EPT 违规、页面修改日志满事件、SPP 相关事件和指令超时而导致的 VM Exits,由于 IRET 导致的 NMI 解除阻塞保存在退出限定的位 12 中(第 28.2.1 节)。

(由于 APIC 访问和 EPT 错误配置,IRET 的执行还可能导致 VM Exits。这些 VM Exits不会报告有关 IRET 导致的 NMI 解锁的信息。)

第 25.9.3 节定义了包含 VM Exits信息的字段,这些退出是在通过 IDT 传递事件时以及由于以下任一情况而发生的:

这些字段用于在传递作为 VM entry的一部分注入的事件期间发生的 VM Exits(请参阅第 27.6.1.2 节)。

在以下任何情况下,事件传递期间不认为发生 VM Exits:

以下各项详细说明了这些字段的使用:

IDT 向量信息(表 25-20 中给出的格式)。以下各项详细说明了如何为事件传递期间发生的 VM Exits建立此字段:

如果在异常传递期间发生 VM Exits,则位 7:0 接收异常向量(最多 31)。如果在传送 NMI 期间发生 VM Exits,则位 7:0 将设置为 2。如果在传送外部中断期间发生 VM Exits,则位 7:0 接收向量。

位 10:8 设置为指示发生 VM Exits时传递的事件类型:0(外部中断)、2(不可屏蔽中断)、3(硬件异常)、4(软件中断)、5(特权软件中断)或6(软件异常)。

硬件异常包括除以下情况之外的所有异常:

INT1指令产生的调试异常(#DB);这些是特权软件例外。 (其他调试异常被视为硬件异常,就像在 enclave 模式下执行 INT1 引起的异常一样。)

断点异常(#BP;由 INT3 生成)和溢出异常(#OF;由 INTO 生成);这些是软件例外情况。 (飞地模式下发生的 #BP 被视为硬件异常。)

超出 BOUND 范围的异常(#BR;由 BOUND 生成)和由 UD0、UD1 和 UD2 生成的无效操作码异常(#UD)是硬件异常。

如果在发送硬件异常期间发生 VM Exits(该异常可能会在堆栈上发送错误代码),则位 11 将设置为 1。如果逻辑处理器处于实地址模式 (CR0.PE=0) 时发生 VM Exits,则该位始终为 0。2 如果位 11 设置为 1,则错误代码将放置在 IDT 向量错误代码中(见下文)。

位 12 未定义。

位 30:13 始终设置为 0。

位 31 始终设置为 1。

对于其他 VM 出口,该字段被标记为无效(通过清除位 31)并且该字段的其余部分未定义。

IDT 向量错误代码。

第 25.9.4 节定义了包含由于指令执行而发生的 VM Exits信息的字段。 (VM Exits指令长度也用于在软件中断或软件异常传递期间发生的 VM Exits。)以下各项详细说明了它们的使用。

在上述所有情况下,该字段接收其执行导致 VM Exits的指令(包括任何指令前缀)的字节长度 (1–15)(有关一个例外,请参阅下一段)。

在传送软件中断、特权软件异常或软件异常期间遇到的 VM Exits情况包括在传送作为 VM entry的一部分注入的事件期间遇到的情况(参见第 27.6.1.2 节)。如果原始事件作为 VM entries的一部分注入,则该字段接收 VM entries指令长度的值。

除上述项目中列出的所有 VM 出口均未定义此字段。

如果 VM Exits发生在 enclave 模式下,则该字段将被清除(前面的项目均不适用)。

VM-exit指令信息。对于由于尝试执行 INS、INVEPT、INVPCID、INVVPID、LIDT、LGDT、LLDT、LOADIWKEY、LTR、OUTS、RDRAND、RDSEED、SIDT、SGDT、SLDT、STR、VMCLEAR、VMPTRLD、VMPTRST、VMREAD、VMWRITE 而导致 VM ExitsVMXON、XRSTORS 或 XSAVES,该字段接收有关导致 VM Exits的指令的信息。该字段的格式取决于导致VM退出的指令的标识:

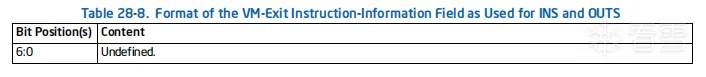

对于由于尝试执行 INS 或 OUTS 而导致 VM Exits,该字段的格式如表 28-8 所示

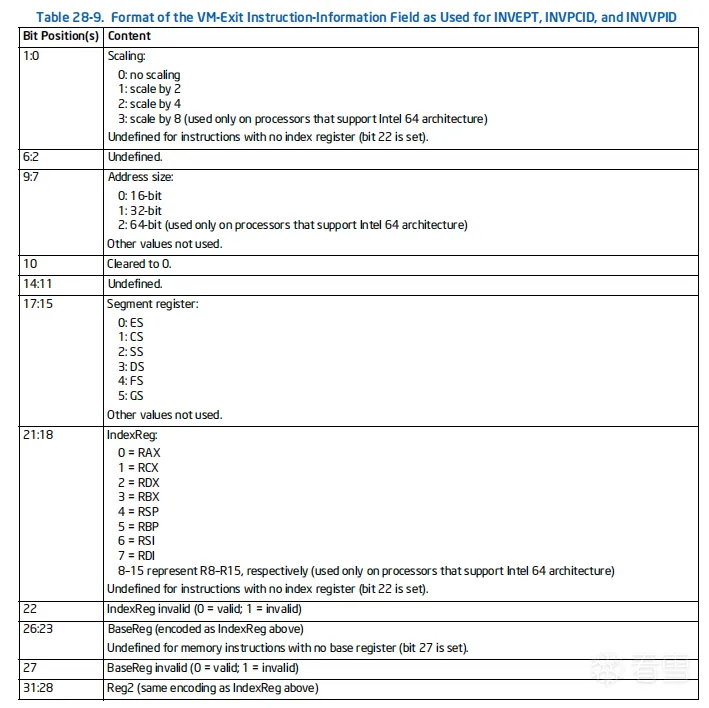

对于由于尝试执行 INVEPT、INVPCID 或 INVVPID 而导致 VM Exits,该字段的格式如表 28-9 所示。

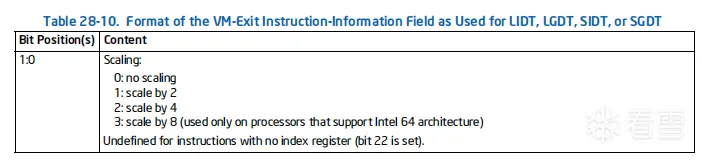

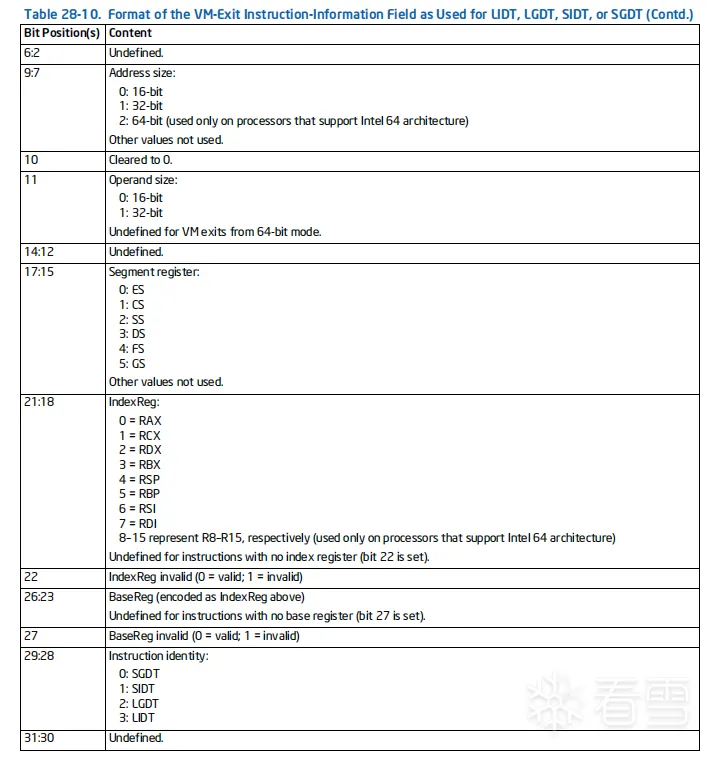

对于由于尝试执行 LIDT、LGDT、SIDT 或 SGDT 而导致 VM Exits,该字段的格式如表 28-10 所示

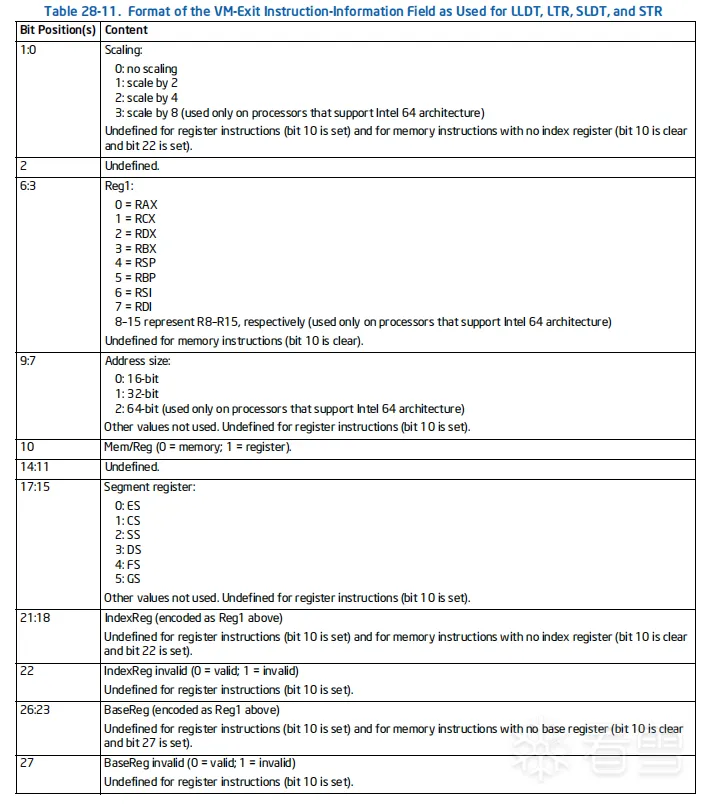

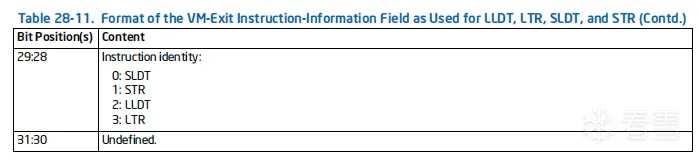

对于由于尝试执行 LLDT、LTR、SLDT 或 STR 而导致 VM Exits,该字段的格式如表 28-11 所示。

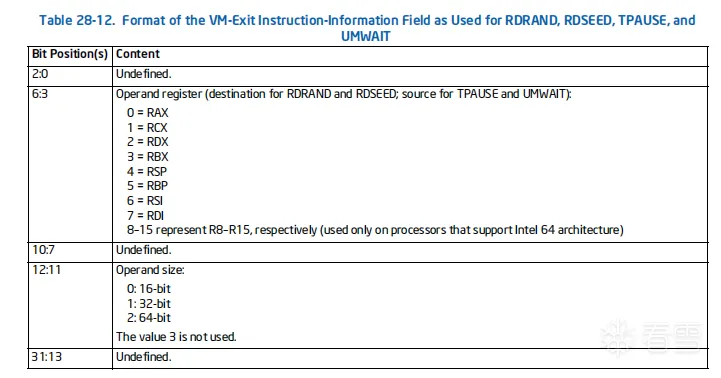

对于由于尝试执行 RDRAND、RDSEED、TPAUSE 或 UMWAIT 而导致 VM Exits,该字段的格式如表 28-12 所示。

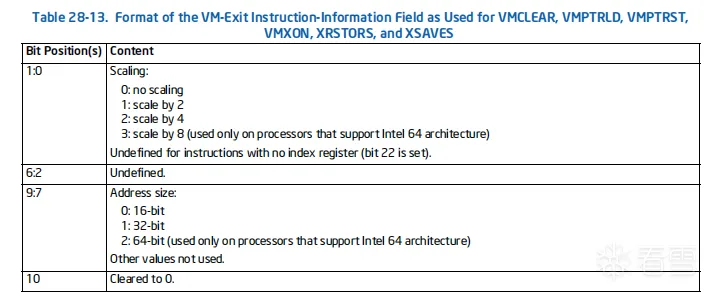

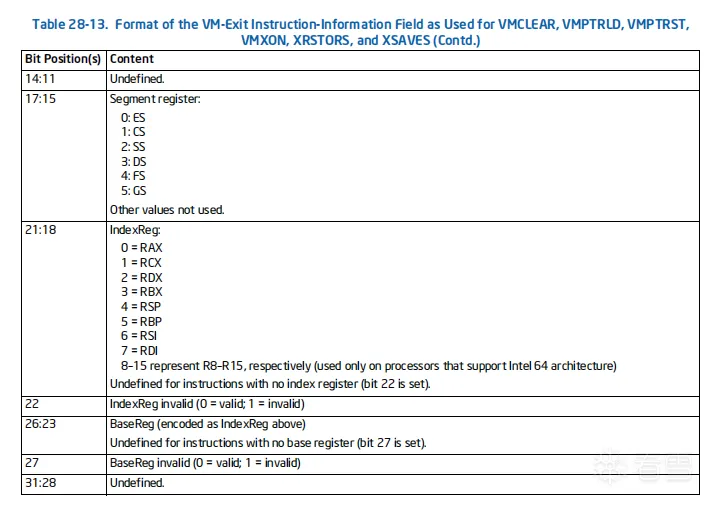

对于由于尝试执行 VMCLEAR、VMPTRLD、VMPTRST、VMXON、XRSTORS 或 XSAVES 导致的 VM Exits,该字段的格式如表 28-13 所示。

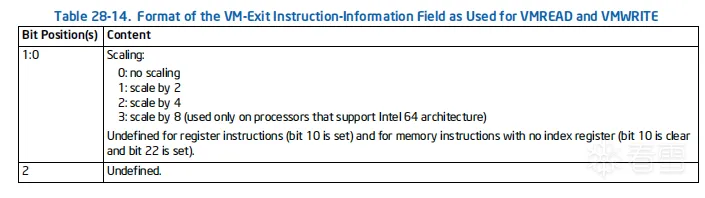

对于由于尝试执行 VMREAD 或 VMWRITE 而导致 VM Exits,该字段的格式如表 28-14 所示。

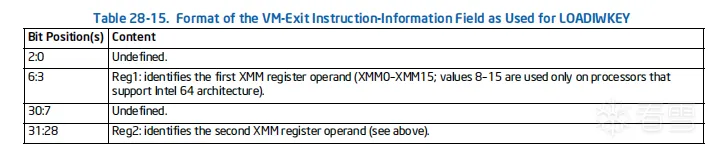

对于由于尝试执行 LOADIWKEY 而导致 VM Exits,该字段的格式如表 28-15 所示。

对于所有其他 VM Exits,该字段未定义,除非 VM Exits发生在 enclave 模式下,在这种情况下该字段将被清除

I/O RCX、I/O RSI、I/O RDI、I/O RIP。除了由于 I/O 指令退出后立即到达的系统管理中断 (SMI) 导致的 SMM VM Exits之外,这些字段未定义。参见第 32.15.2.3 节。请注意,如果 VM Exits发生在 enclave 模式下,则这些字段都会被清除。

VM 出口将处理器状态的某些组件保存到 VMCS 的客户状态区域中的相应字段中(参见第 25.4 节)。在支持 Intel 64 架构的处理器上,无论 VM Exits之前和之后逻辑处理器的模式如何,都会保存每个自然宽度字段(请参阅第 25.11.2 节)的完整值。

一般来说,保存的状态是VM退出开始时逻辑处理器中的状态。有关当时发生哪些架构更新的讨论,请参见第 28.1 节。

第 28.3.1 节到第 28.3.4 节提供了如何保存处理器状态的各个组成部分的详细信息。这些部分引用与处理器状态相对应的 VMCS 字段。除非另有说明,否则这些引用是指客区区域中的字段。

某些控制寄存器、调试寄存器和MSR的内容保存如下:

对于每个段寄存器(CS、SS、DS、ES、FS、GS、LDTR 或 TR),为基址、段限制和访问权限保存的值基于寄存器是否不可用(请参见第 25.4 节) .1) VM退出前:

GDTR 和 IDTR 寄存器的内容保存到相应的基址和限制字段中。

RIP、RSP、RFLAGS 和 SSP(影子堆栈指针)寄存器的内容保存如下:

guest 未登记状态对应的信息保存如下:

活动状态字段在 VM Exits之前与逻辑处理器的活动状态一起保存。1 有关导致 VM Exits的事件如何影响活动状态的详细信息,请参见第 28.1 节。如果VM退出发生在用户中断通知处理期间(参见第7.5.2节),并且逻辑处理器在用户中断通知处理之后进入HLT状态,则保存的活动状态为“HLT”。

保存可中断状态字段以反映VM退出之前逻辑处理器的可中断性

此类VM退出包括由中断、不可屏蔽中断、系统管理中断、INIT信号和飞地模式中发生的异常以及在飞地模式中发生的此类事件的传递期间遇到的异常引起的退出。

与 VM entries注入的事件的传递相关的 VM Exits使该位保持不变。

对于所有 VM Exits,挂起的调试异常字段都会保存为清除状态,以下情况除外:

对于不清除该字段的 VM Exits,保存的值确定如下:

如果位 3:0 中的每一位对应于匹配的断点,则可以对其进行设置。即使 DR7 中未启用相应的断点,情况也可能如此。

假设 VM Exits是由于 INIT 信号、机器检查异常或 SMI 导致的;或者 VM Exits具有基本退出原因“TPR 低于阈值”或“监视器陷阱标志”。在这种情况下,保存的值设置与 VM Exits时未决的任何调试异常的原因相对应的位。

如果 VM Exits在 VM entry后立即发生,则保存的值可能与 VM entry时加载的值匹配(请参阅第 27.7.3 节)。否则,适用以下条款:

在以下任一情况下,位 12(启用断点)设置为 1:

在其他情况下,位 12 被清除为 0。

如果在以下任一情况下 RFLAGS.TF = 1,则设置位 14 (BS):

如果在已启用 RTM 事务区域的高级调试的情况下在 RTM 区域内发生调试异常 (#DB) 或断点异常 (#BP),则设置位 16 (RTM)。 (这不适用于具有基本退出原因“监视器陷阱标志”的 VM Exits。)

假设 VM Exits是由于其他原因(但不是调试异常)并且在 MOV SS 阻止调试异常时发生。在这种情况下,保存的值设置与 VM Exits时未决的任何调试异常的原因相对应的位。如果VM退出发生在VM进入之后(在VMX非root操作中没有执行任何指令),则保存的值可能与VM进入时加载的值匹配(参见第27.7.3节)。否则,适用以下条款:

该字段中的保留位被清除。

如果“保存VMX抢占定时器值”VM退出控制为1,则定时器的值被保存到VMX抢占定时器值字段中。这是在 VM entries上从该字段加载的值,随后递减(参见第 26.5.1 节)。由于定时器到期而退出的 VM 保存值 0。如果在 VM Exits期间定时器到期,其他 VM Exits也可能保存值 0。 (如果“保存VMX抢占计时器值”VM退出控制为0,则VM退出不会修改VMX抢占计时器值字段的值。)

如果逻辑处理器支持“启用 EPT”VM 执行控制的 1 设置,则值将保存到四 (4) 个 PDPTE 字段中,如下所示:

将处理器状态保存到客户状态区域后,MSR 的值可以存储到 VM Exits MSR 存储区域(参见第 25.7.2 节)。具体来说,该区域中的每个条目(最多为 VM Exits MSR 存储计数中指定的数量)通过将位 31:0 索引的 MSR 值(因为它们将由 RDMSR 读取)存储到位中来按顺序处理127:64。在以下任一情况下,条目处理失败:

如果任何条目的处理失败,则会发生 VMX 中止。参见第 28.7 节。

处理器状态在 VM Exits时通过以下方式更新:

该加载可以以任何顺序执行。

在支持 Intel 64 架构的处理器上,无论 VM Exits之前和之后逻辑处理器的模式如何,都会加载每个加载的 64 位字段的完整值(例如 GDTR 的基地址)。

host状态的加载详见第 28.5.1 节至第 28.5.5 节。这些部分引用与处理器状态相对应的 VMCS 字段。除非另有说明,这些引用是指Host-state区域中的字段。

仅当“host地址空间大小”VM Exits控制为 1 时,逻辑处理器在 VM Exits后才处于 IA-32e 模式。如果逻辑处理器在 VM Exits之前处于 IA-32e 模式且此控制为 0,发生 VMX 中止。参见第 28.7 节。

除了加载host状态之外,VM 还退出清晰的地址范围监控(第 28.5.6 节)。

在本节中描述的状态加载之后,VM退出可以从VM退出MSR加载区域加载MSR(参见第28.6节)。此加载仅在本节中描述的状态加载之后发生。

VM Exits为控制寄存器、调试寄存器和一些 MSR 加载新值:

CR0、CR3 和 CR4 分别从 CR0 字段、CR3 字段和 CR4 字段加载,但以下情况除外:

DR7 设置为 400H。

如果“清除 UINV”VM Exits控制为 1,VM Exits将清除 UINV

以下MSR的建立如下:

IA32_DEBUGCTL MSR 被清除为 00000000_00000000H

IA32_SYSENTER_CS MSR 是从 IA32_SYSENTER_CS 字段加载的。由于该字段只有 32 位,因此 MSR 的位 63:32 被清除为 0。

IA32_SYSENTER_ESP 和 IA32_SYSENTER_EIP MSR 分别从 IA32_SYSENTER_ESP 和 IA32_SYSENTER_EIP 字段加载。

如果处理器不支持Intel 64架构,这些字段只有32位; MSR 的位 63:32 被清除为 0。

如果处理器支持 N < 64 个线性地址位的 Intel 64 架构,则 63:N 位中的每一位都将设置为位 N–1 的值。

以下步骤在支持 Intel 64 架构的处理器上执行:

如果“加载 IA32_PERF_GLOBAL_CTRL”VM Exits控制为 1,则从 IA32_PERF_GLOBAL_CTRL 字段加载 IA32_PERF_GLOBAL_CTRL MSR。该 MSR 中保留的位以其保留值进行维护。

如果“加载 IA32_PAT”VM Exits控制为 1,则从 IA32_PAT 字段加载 IA32_PAT MSR。该 MSR 中保留的位以其保留值进行维护。

如果“加载 IA32_EFER”VM Exits控制为 1,则从 IA32_EFER 字段加载 IA32_EFER MSR。该 MSR 中保留的位以其保留值进行维护。

如果“清除 IA32_BNDCFGS”VM Exits控制为 1,则 IA32_BNDCFGS MSR 被清除为 00000000_00000000H;否则不予修改。

如果“清除 IA32_RTIT_CTL”VM Exits控制为 1,则 IA32_RTIT_CTL MSR 被清除为 00000000_00000000H;否则不予修改。

如果“加载 CET”VM Exits控制为 1,则分别从 IA32_S_CET 和 IA32_INTERRUPT_SSP_TABLE_ADDR 字段加载 IA32_S_CET 和 IA32_INTERRUPT_SSP_TABLE_ADDR MSR。

如果处理器不支持Intel 64架构,这些字段只有32位; MSR 的位 63:32 被清除为 0。

如果处理器支持 N < 64 个线性地址位的 Intel 64 架构,则 63:N 位中的每一位都将设置为位 N–1 的值。

如果“加载 PKRS”VM Exits控制为 1,则从 IA32_PKRS 字段加载 IA32_PKRS MSR。该 MSR 的位 63:32 保持为零。

除了 FS.base 和 GS.base 之外,这些 MSR 中的任何一个如果出现在 VM Exits MSR 加载区域中,随后都会被覆盖。参见第 28.6 节。

每个寄存器CS、SS、DS、ES、FS、GS和TR的加载如下(LDTR的处理见下文):

选择器是从选择器字段加载的。如果其选择器加载为零,则该段不可用。第 27.2.3 节中指定的检查限制了可以加载的选择器值。特别是,CS 和 TR 永远不会加载零,因此永远不会不可用。仅在支持 Intel 64 架构的处理器上并且仅当 VM Exits到 64 位模式时(64 位模式允许使用标记为不可用的段),SS 才可以加载为零。

基地址设置如下:

CS。清零。

SS、DS 和 ES。如果该段不可用,则未定义;否则清零

FS 和 GS。如果段不可用且 VM Exits不是 64 位模式,则未定义(但在支持 Intel 64 架构的处理器上,规范);否则,从基地址字段加载。

如果处理器支持 Intel 64 架构并且处理器支持 N < 64 线性地址位,则 63:N 位中的每一位都设置为位 N–1.1 的值。为 FS 和 GS 基地址加载的值也显示在FS.base 和 GS.base MSR。

TR。从host状态区域加载。如果处理器支持 Intel 64 架构并且处理器支持 N < 64 个线性地址位,则每个位 63:N 将设置为位 N–1 的值。

段限制设置如下:

类型字段和S位设置如下:

DPL 设置如下:

P 位设置如下:

在支持 Intel 64 架构的处理器上,CS.L 加载了“host地址空间大小”VM Exits控制的设置。因为该控件的值也被加载到 IA32_EFER.LMA(请参阅第 28.5.1 节),所以任何 VM Exits都不会进入兼容模式(这需要 IA32_EFER.LMA = 1 且 CS.L = 0)。

D B。

G。

host状态区域不包含 LDTR 的选择器字段。 LDTR 在所有 VM 出口上按如下方式建立:选择器被清除为 0000H,该段被标记为不可用,否则未定义(尽管基地址始终是规范的)。

GDTR 和 IDTR 的基地址从 GDTR 基地址字段和 IDTR 基地址字段加载

场,分别。如果处理器支持 Intel 64 架构并且处理器支持 N < 64 个线性地址位,则每个基地址的位 63:N 中的每一位都将设置为该基地址的位 N–1 的值。 GDTR 和 IDTR 限制均设置为 FFFFH。

RIP和RSP分别从RIP字段和RSP字段加载。 RFLAGS 被清除,但位 1 除外,该位始终被置位。

如果“加载 CET”VM Exits控制为 1,则从 SSP 字段加载 SSP(影子堆栈指针)

如果 CR0.PG = 1、CR4.PAE = 1 且 IA32_EFER.LMA = 0,则逻辑处理器使用 PAE 分页。请参阅英特尔® 64 和 IA-32 架构软件开发人员手册第 3A.1 卷第 4.4 节。当使用 PAE 分页时,CR3 中的物理地址引用页目录指针表条目 (PDPTE) 表。当使用 PAE 分页时,MOV 到 CR3 会检查 PDPTE 的有效性,如果有效,则将它们加载到处理器中(加载到内部非体系结构寄存器中)。

如果 (1) 在 VMCS 的host状态区域中的 CR4 字段中设置了第 5 位(对应于 CR4.PAE),则 VM Exits到使用 PAE 分页的 VMM; (2)“host地址空间大小”VM退出控制为0。这样的VM退出可以检查由VMCS的host状态区域中的CR3字段引用的PDPTE的有效性。如果 (1) PAE 分页在 VM Exits之前未使用,则此类 VM Exits必须检查其有效性; (2) CR3 的值由于 VM Exits而发生变化。到不使用 PAE 分页的 VMM 的 VM Exits不得检查 PDPTE 的有效性。

检查 PDPTE 有效性的 VM 出口使用的检查与使用 PAE 分页时通过 MOV 加载 CR3 时使用的检查相同。如果 MOV 到 CR3 会由于要加载的 PDPTE(例如,因为设置了保留位)而导致一般保护异常,则会发生 VMX 中止(请参阅第 28.7 节)。如果使用 PAE 的 VMM 的 VM Exits不会导致 VMX 中止,则 PDPTE 会像 MOV 到 CR3 一样加载到处理器中,并使用 VM 出口加载的 CR3 值。

VM Exits会影响逻辑处理器的非寄存器状态,如下所示:

第 29.4 节描述了 VMX 架构如何控制逻辑处理器如何管理 TLB 和分页结构高速缓存中的信息。以下项目详细介绍了VM如何退出使缓存的映射无效:

Intel 64 和 IA-32 架构允许软件使用 MONITOR 和 MWAIT 指令监视指定的地址范围。请参阅英特尔® 64 和 IA-32 架构软件开发人员手册第 3A 卷中的第 9.10.4 节。 VM Exits清除任何可能有效的地址范围监控。

VM出口可以从VM出口MSR加载区域加载MSR(参见第25.7.2节)。具体来说,该区域中的每个条目(最多达到 VM Exits MSR 加载计数中指定的数量)通过加载由位 31:0 索引的 MSR 以及位 127:64 的内容来按顺序处理,因为它们将由WRMSR。

如果出现以下任一情况,则条目处理失败:

如果任何条目的处理失败,则会发生 VMX 中止。参见第 28.7 节

如果任何 MSR 的加载方式在架构上需要 TLB 刷新,则 TLB 会被更新,以便在 VM Exits后,逻辑处理器不会使用转换之前缓存的任何转换。

VM Exits期间遇到的问题会导致 VMX 中止。 VMX 中止使逻辑处理器进入关闭状态,如下所述。

VMX 中止不会修改任何活动 VMCS 的 VMCS 区域中的 VMCS 数据。因此,在 VMX 中止后,这些数据的内容值得怀疑。

在 VMX 中止时,逻辑处理器在错误配置导致失败的 VMCS 的 VMCS 区域中的字节偏移量 4 处保存非零 32 位 VMX 中止指示符字段(请参阅第 25.2 节)。使用以下值:

其中一些原因与从host状态区域加载状态期间的失败相对应。由于此类状态的加载可以按任何顺序完成(请参阅第 28.5 节),因此 VM Exits可能会因多种原因导致 VMX 中止(例如,当前 VMCS 可能已损坏,host PDPTE 可能未正确配置) 。在这种情况下,VMX 中止指示器可能对应于这些原因中的任何一个。

逻辑处理器从不读取 VMCS 区域中的 VMX 中止指示符,并且仅使用上述非零值之一写入它。 VMX 中止指示器允许一个逻辑处理器上的软件诊断另一逻辑处理器上的 VMX 中止。因此,建议在 VMX root operation中运行的软件将其使用的任何 VMCS 的 VMCS 区域中的 VMX 中止指示器归零。

保存 VMX 中止指示符后,经历 VMX 中止的逻辑处理器的操作取决于该逻辑处理器是否处于 SMX 操作中:

如果 VM Exits期间发生计算机检查事件,则会发生以下情况之一:

处理机器检查事件就好像它发生在虚拟机退出之前一样:

机器检查事件在 VM Exits完成后处理:

生成 VMX 中止(请参阅第 28.7 节)。逻辑处理器会像通常那样阻止事件

VMX 中止。 VMX 中止指示器为 5,表示“VM Exits期间的机器检查事件”。

如果在加载任何host状态之后发生机器检查事件,则不使用第一个选项。仅当 VM entries能够加载所有host状态时才使用第二个选项。

如果 VM Exits以 CR4.UINTR = IA32_EFER.LMA = 1 且 UIRR ≠ 0 完成,则会导致识别待处理的用户中断;否则,不会识别待处理的用户中断。

- 28 虚拟机退出

- 28.1 虚拟机退出前的架构状态

- 28.2 记录VM-EXIT信息和更新VM-ENTRY控制字段

- 28.2.1 基本 VM Exits信息

- 28.2.2 由于向量事件导致 VM Exits的信息

- 28.2.3 有关 IRET 导致的 NMI 解锁的信息

- 28.2.4 事件传递期间 VM Exits的信息

- 28.2.5 由于指令执行而导致 VM Exits的信息

- 28.3 保存guest状态

- 28.3.1 保存控制寄存器、调试寄存器和 MSR

- 28.3.2 保存段寄存器和描述符表寄存器

- 28.3.3 保存RIP、RSP、RFLAGS和SSP

- 28.3.4 保存非注册状态

- 28.4 保存MSRS

- 28.5 加载host状态

- 28.5.1 加载host控制寄存器、调试寄存器、MSR

- 28.5.2 加载host段和描述符表寄存器

- 28.5.3 加载hostRIP、RSP、RFLAGS和SSP

- 28.5.4 检查并加载host页目录指针表条目

- 28.5.5 更新非注册状态

- 28.5.6 清除地址范围监控

- 28.6 加载 MSRS

- 28.7 VMX 中止

- 28.8 VM退出期间的机器检查事件

- 28.9 VM退出后的用户中断识别

- 第24章 INTRODUCTION TO VIRTUAL MACHINE EXTENSIONS

- 第25章 VIRTUAL MACHINE CONTROL STRUCTURES

- 第26章 VMX NON-ROOT OPERATION

- 第27章 VM Entries

- 第28章 VM EXITS

- 第29章 VMX SUPPORT FOR ADDRESS TRANSLATION

- 28 虚拟机退出

- 28.1 虚拟机退出前的架构状态

- 28.2 记录VM-EXIT信息和更新VM-ENTRY控制字段

- 28.2.1 基本 VM Exits信息

- 28.2.2 由于向量事件导致 VM Exits的信息

- 28.2.3 有关 IRET 导致的 NMI 解锁的信息

- 28.2.4 事件传递期间 VM Exits的信息

- 28.2.5 由于指令执行而导致 VM Exits的信息

- 28.3 保存guest状态

- 28.3.1 保存控制寄存器、调试寄存器和 MSR

- 28.3.2 保存段寄存器和描述符表寄存器

- 28.3.3 保存RIP、RSP、RFLAGS和SSP

- 28.3.4 保存非注册状态

- 28.4 保存MSRS

- 28.5 加载host状态

- 28.5.1 加载host控制寄存器、调试寄存器、MSR

- 28.5.2 加载host段和描述符表寄存器

- 28.5.3 加载hostRIP、RSP、RFLAGS和SSP

- 28.5.4 检查并加载host页目录指针表条目

- 28.5.5 更新非注册状态

- 28.5.6 清除地址范围监控

- 28.6 加载 MSRS

- 28.7 VMX 中止

- 28.8 VM退出期间的机器检查事件

- 28.9 VM退出后的用户中断识别

- 处理器状态的加载部分基于host状态区域和一些虚拟机退出控制。对于激活 SMI 和 SMM 的双监视器处理的 SMM VM Exits,不执行此步骤。有关此类 VM 出口如何加载处理器状态的信息,请参阅第 32.15.6 节。

- 地址范围监控已清除。

- 如果在异常位图中设置了与该异常相对应的位,则该异常会直接导致 VM Exits。如果“NMI 退出”VM 执行控制为 1,则不可屏蔽中断 (NMI) 会直接导致 VM Exits。如果“外部中断退出”VM 执行控制为 1,则外部中断会直接导致 VM Exits。当逻辑处理器处于等待 SIPI 活动状态时到达的启动 IPI (SIPI) 会直接导致 VM Exits。当处理器未处于等待 SIPI 活动状态时到达的 INIT 信号会导致 VM 直接退出。

- 异常、NMI、外部中断或软件中断会间接导致 VM Exits,如果它不直接这样做,但事件的传递会导致嵌套异常、双重故障、任务切换、APIC 访问(请参阅第 30.4 节)、EPT 违规, EPT 配置错误、页面修改日志满事件(请参阅第 29.3.6 节)或 SPP 相关事件(请参阅第 29.3.4 节)会导致 VM Exits。

- 如果事件导致 VM Exits(直接或间接),则该事件会导致 VM Exits。

-

如果事件直接导致 VM Exits,则它不会像没有导致 VM Exits时那样更新体系结构状态:

-

调试异常不会更新 DR6、DR7 或 IA32_DEBUGCTL。 (有关调试异常性质的信息保存在退出限定字段中。)

-

页面错误不会更新 CR2。 (导致页面错误的线性地址保存在退出限定字段中。)

-

NMI 会导致后续 NMI 被阻止,但仅限于 VM Exits完成之后。

-

外部中断不会确认中断控制器,并且中断保持挂起状态,除非“退出时确认中断”VM-exit 控制为 1。在这种情况下,中断控制器被确认并且中断不再挂起。

-

当任务切换导致 VM Exits时,DR7 中的标志 L0 – L3(位 0、位 2、位 4 和位 6)不会被清除。

-

如果任务切换导致 VM Exits,则任务切换不会修改以下任何内容: 旧任务状态段 (TSS);新的 TSS;旧的 TSS 描述符;新的 TSS 描述符; RFLAGS.NT1;或 TR 寄存器。

-

如果事件直接导致 VM Exits,则不会创建最后异常记录。

-

如果机器检查异常直接导致VM退出,这不会阻止机器检查MSR的更新。这些是由机器检查事件本身更新的,而不是由生成的机器检查异常更新的。

-

如果逻辑处理器处于非活动状态(参见第 25.4.2 节)并且不执行指令,则某些事件可能会被阻止,但其他事件可能会将逻辑处理器返回到活动状态。未阻止事件可能会导致 VM Exits。2 如果未阻止事件直接导致 VM Exits,则仅在 VM Exits完成后才会返回到活动状态。3 VM Exits会生成通常在活动状态处于活动状态时生成的任何特殊总线周期。从该活动状态进入。

MTF VM 出口(参见第 26.5.2 节和第 27.7.8 节)在 HLT 活动状态下不会被阻止。如果在 HLT 活动状态下发生 MTF VM Exits,则逻辑处理器仅在 VM Exits完成后才返回到活动状态。 MTF VM退出被阻塞在关闭状态和等待SIPI状态。

-

-

如果某个事件间接导致 VM Exits,则该事件会更新体系结构状态:

- 调试异常会更新 DR6、DR7 和 IA32_DEBUGCTL MSR。没有调试异常被视为待处理。

- 页面错误更新 CR2。

- NMI 会导致后续 NMI 在 VM Exits开始之前被阻止。

- 外部中断确认中断控制器并且中断不再待处理。

- 如果逻辑处理器已处于不活动状态,则它进入活动状态,并且在VM退出开始之前,生成通常在从该活动状态进入活动状态时生成的任何特殊总线周期。

- 当 VM Exits开始时,STI 或 MOV SS 不会阻塞

- 通常作为通过 IDT 交付的一部分进行更新的处理器状态(CS、RIP、SS、RSP、RFLAGS)不会被修改。但是,事件的不完整传递可能会写入堆栈。

- 最后异常记录的处理取决于实现:

- 某些处理器在开始通过 IDT 传递事件时(在遇到嵌套异常之前)会生成最后异常记录。即使事件遇到导致 VM Exits的嵌套异常(包括嵌套异常导致三重故障的情况),此类处理器也会执行此更新。

- 其他处理器会延迟创建最后一个异常记录,直到事件传递成功到达某个事件处理程序(可能在一个或多个嵌套异常之后)。如果在到达事件处理程序之前发生 VM Exits或三重故障,此类处理器不会更新最后的异常记录。

-

如果“虚拟 NMI”VM 执行控制为 1,则 VM entries注入 NMI,并且 NMI 的传递会导致嵌套异常、双重错误、任务切换、EPT 违规、EPT 配置错误、页面修改日志满事件或SPP 相关事件或导致 VM Exits的 APIC 访问、虚拟 NMI 阻止在 VM Exits开始之前生效。

-

如果 VM Exits是由于 IRET 执行期间遇到的故障、EPT 违规、EPT 错误配置、页面修改日志满事件或 SPP 相关事件导致的,并且“NMI 退出”VM 执行控制为 0,则任何阻塞在 VM Exits开始之前,由 NMI 清除。然而,之前被NMI阻止的状态可以记录在退出资格中或者VM-退出中断信息字段中;参见第 28.2.3 节。

-

假设 VM Exits是由 x87 FPU 浮点错误 (#MF) 直接引起的,或者是由以下任何事件引起的(如果该事件由于 x87 FPU 浮点错误而被解除阻止(并具有优先级): INIT信号、外部中断、NMI、SMI;或机器检查异常。在这些情况下,当 VM Exits开始时,STI 或 MOV SS 不会阻塞。

-

通常,当通过IDT传递事件时,可以进行最后分支记录。但是,如果此类事件导致 VM 在交付完成之前退出,则不会创建最后一个分支记录。

-

如果机器检查异常导致 VM Exits,则处理器状态是可疑的,并且可能导致可疑状态被保存到guest 状态区域。在恢复因机器检查异常导致 VM Exits的 guest 虚拟机之前,VM 监视器应查阅 IA32_MCG_STATUS MSR 中的 RIPV 和 EIPV 位。

-

以下VM退出被认为是在指令执行后发生:

-

由于调试陷阱(单步、I/O 断点和数据断点)导致 VM Exits。

-

VM 因调试异常(数据断点)而退出,该异常的识别因 MOV SS 的阻塞而延迟。

-

由于某些机器检查异常而导致虚拟机退出。

-

当“CR8加载退出”VM执行控制为0并且“使用TPR影子”VM执行控制为1时,由于执行MOV到CR8,类陷阱VM退出(参见第30.3节)。 (此类 VM Exits只能在 64 位模式下发生,因此只能在支持 Intel 64 架构的处理器上发生。)

-

当“使用 MSR 位图”VM 执行控制为 1 时,由于执行 WRMSR,类陷阱 VM Exits; ECX的取值范围为800H~8FFH;低MSR的写位图中ECX值对应的位为0; “虚拟化 x2APIC 模式”VM 执行控制为 1。请参见第 30.5 节。

-

由 APIC 写入仿真(参见第 30.4.3.2 节)引起的 VM Exits,该仿真是由 APIC 访问(作为指令执行的一部分)引起的。

对于这些VM退出,指令对架构状态的修改在VM退出发生之前完成。此类修改包括对逻辑处理器的可中断性状态的修改(参见表 25-3)。如果在指令执行之前已经被 MOV SS、POP SS 或 STI 阻塞,则该阻塞不再有效。

-

-

调试异常不会更新 DR6、DR7 或 IA32_DEBUGCTL。 (有关调试异常性质的信息保存在退出限定字段中。)

-

页面错误不会更新 CR2。 (导致页面错误的线性地址保存在退出限定字段中。)

-

NMI 会导致后续 NMI 被阻止,但仅限于 VM Exits完成之后。

-

外部中断不会确认中断控制器,并且中断保持挂起状态,除非“退出时确认中断”VM-exit 控制为 1。在这种情况下,中断控制器被确认并且中断不再挂起。

-

当任务切换导致 VM Exits时,DR7 中的标志 L0 – L3(位 0、位 2、位 4 和位 6)不会被清除。

-

如果任务切换导致 VM Exits,则任务切换不会修改以下任何内容: 旧任务状态段 (TSS);新的 TSS;旧的 TSS 描述符;新的 TSS 描述符; RFLAGS.NT1;或 TR 寄存器。

-

如果事件直接导致 VM Exits,则不会创建最后异常记录。

-

如果机器检查异常直接导致VM退出,这不会阻止机器检查MSR的更新。这些是由机器检查事件本身更新的,而不是由生成的机器检查异常更新的。

-

如果逻辑处理器处于非活动状态(参见第 25.4.2 节)并且不执行指令,则某些事件可能会被阻止,但其他事件可能会将逻辑处理器返回到活动状态。未阻止事件可能会导致 VM Exits。2 如果未阻止事件直接导致 VM Exits,则仅在 VM Exits完成后才会返回到活动状态。3 VM Exits会生成通常在活动状态处于活动状态时生成的任何特殊总线周期。从该活动状态进入。

MTF VM 出口(参见第 26.5.2 节和第 27.7.8 节)在 HLT 活动状态下不会被阻止。如果在 HLT 活动状态下发生 MTF VM Exits,则逻辑处理器仅在 VM Exits完成后才返回到活动状态。 MTF VM退出被阻塞在关闭状态和等待SIPI状态。

- 调试异常会更新 DR6、DR7 和 IA32_DEBUGCTL MSR。没有调试异常被视为待处理。

- 页面错误更新 CR2。

- NMI 会导致后续 NMI 在 VM Exits开始之前被阻止。

- 外部中断确认中断控制器并且中断不再待处理。

- 如果逻辑处理器已处于不活动状态,则它进入活动状态,并且在VM退出开始之前,生成通常在从该活动状态进入活动状态时生成的任何特殊总线周期。

- 当 VM Exits开始时,STI 或 MOV SS 不会阻塞

- 通常作为通过 IDT 交付的一部分进行更新的处理器状态(CS、RIP、SS、RSP、RFLAGS)不会被修改。但是,事件的不完整传递可能会写入堆栈。

- 最后异常记录的处理取决于实现:

- 某些处理器在开始通过 IDT 传递事件时(在遇到嵌套异常之前)会生成最后异常记录。即使事件遇到导致 VM Exits的嵌套异常(包括嵌套异常导致三重故障的情况),此类处理器也会执行此更新。

- 其他处理器会延迟创建最后一个异常记录,直到事件传递成功到达某个事件处理程序(可能在一个或多个嵌套异常之后)。如果在到达事件处理程序之前发生 VM Exits或三重故障,此类处理器不会更新最后的异常记录。

- 某些处理器在开始通过 IDT 传递事件时(在遇到嵌套异常之前)会生成最后异常记录。即使事件遇到导致 VM Exits的嵌套异常(包括嵌套异常导致三重故障的情况),此类处理器也会执行此更新。

- 其他处理器会延迟创建最后一个异常记录,直到事件传递成功到达某个事件处理程序(可能在一个或多个嵌套异常之后)。如果在到达事件处理程序之前发生 VM Exits或三重故障,此类处理器不会更新最后的异常记录。

-

由于调试陷阱(单步、I/O 断点和数据断点)导致 VM Exits。

-

VM 因调试异常(数据断点)而退出,该异常的识别因 MOV SS 的阻塞而延迟。

-

由于某些机器检查异常而导致虚拟机退出。

-

当“CR8加载退出”VM执行控制为0并且“使用TPR影子”VM执行控制为1时,由于执行MOV到CR8,类陷阱VM退出(参见第30.3节)。 (此类 VM Exits只能在 64 位模式下发生,因此只能在支持 Intel 64 架构的处理器上发生。)

-

当“使用 MSR 位图”VM 执行控制为 1 时,由于执行 WRMSR,类陷阱 VM Exits; ECX的取值范围为800H~8FFH;低MSR的写位图中ECX值对应的位为0; “虚拟化 x2APIC 模式”VM 执行控制为 1。请参见第 30.5 节。

-

由 APIC 写入仿真(参见第 30.4.3.2 节)引起的 VM Exits,该仿真是由 APIC 访问(作为指令执行的一部分)引起的。

对于这些VM退出,指令对架构状态的修改在VM退出发生之前完成。此类修改包括对逻辑处理器的可中断性状态的修改(参见表 25-3)。如果在指令执行之前已经被 MOV SS、POP SS 或 STI 阻塞,则该阻塞不再有效。

- RFLAGS 中的以下位被清除:CF、PF、AF、ZF、SF、OF 和 RF。

- FS 和 GS 将恢复到最近的 enclave 条目之前的值。

- RIP 加载了中断的 enclave 线程的 AEP。

- RSP 是从 enclave 的状态保存区域 (SSA) 中的 URSP 字段加载的。

-

退出原因。

-

该字段的位 15:0 包含基本退出原因。它加载了一个数字,指示 VM Exits的一般原因。附录 C 列出了所使用的数字及其含义。

-

如果“过早繁忙影子堆栈”VM Exits控制为 1 并且 VM Exits导致影子堆栈过早繁忙(请参阅第 26.4.3 节),则设置位 25。否则,该位被清除。

-

如果在总线锁定断言之后发生 VM Exits,同时“VMM 总线锁定检测”VM 执行控制为 1,则该字段的位 26 设置为 1。此类 VM Exits包括由于 1 设置而发生的 VM Exits。该控制以及在执行断言总线锁定的指令期间可能发生的其他控制。

-

如果逻辑处理器处于 enclave 模式时发生 VM Exits,则该字段的位 27 设置为 1

此类VM退出包括由中断、不可屏蔽中断、系统管理中断、INIT信号和飞地模式中发生的异常以及在飞地模式中发生的此类事件的传递期间遇到的异常引起的退出。

如果 VM entry所注入的事件的传递发生并且guest 中断状态字段指示飞地中断(该字段的位 4 为 1),则 VM 出口也会设置该位。

-

该字段的其余部分(位 31:28 和位 24:16)被清除为 0(某些 SMM VM 出口可能会设置其中一些位;请参阅第 32.15.2.3 节)。

-

退出资格。由于以下原因而导致虚拟机退出时,会保存此字段:调试异常;页面错误异常;初创企业 IPI (SIPI);执行 I/O 指令后立即到达的系统管理中断 (SMI);任务切换;投资; INVLPG; INVPCID; INVVPID; LGDT;激光损伤检测; LLDT;长期关系; SGDT; SIDT; SLDT; STR; VM清除; VMPTRLD; VMPTRST;虚拟机读取;虚拟机写入; VMXON; WBNVD; WBNOINVD; XRSTORS; X保存;控制寄存器访问; MOV 博士; I/O指令;等待;访问 APIC 访问页面(参见第 30.4 节); EPT 违规行为(参见第 29.3.3.2 节); EOI 虚拟化(参见第 30.1.4 节); APIC 写入仿真(参见第 30.4.3.3 节);页面修改日志已满(参见第 29.3.6 节); SPP 相关事件(参见第 29.3.4 节);和指令超时(参见第 26.2 节)。对于所有其他 VM 出口,该字段被清除。以下项目提供详细信息:

-

对于调试异常,退出限定包含有关调试异常的信息。这

-

对于页错误异常,退出限定包含导致页错误的线性地址。在支持 Intel 64 架构的处理器上,如果逻辑处理器在 VM Exits之前未处于 64 位模式,则清除位 63:32。

如果页错误异常发生在飞地模式下的指令执行期间(而不是在传送飞地模式的事件期间),则退出资格的位 11:0 被清除。

-

对于启动 IPI (SIPI),退出资格包含位 7:0 中的 SIPI 向量信息。退出资格的位 63:8 被清除为 0。

-

对于任务切换,退出限定包含有关任务切换的详细信息,编码如表 28-2 所示。

-

对于 INVLPG,退出限定包含指令的线性地址操作数。

-

在支持 Intel 64 架构的处理器上,如果逻辑处理器在 VM Exits之前未处于 64 位模式,则清除位 63:32。

-

如果 INVLPG 源操作数指定不可用的段,则退出限定中指定的线性地址将与 INVLPG 在未发生 VM Exits时使用的线性地址相匹配。该地址没有在体系结构上定义,并且可能是特定于实现的。

-

-

对于 INVEPT、INVPCID、INVVPID、LGDT、LIDT、LLDT、LTR、SGDT、SIDT、SLDT、STR、VMCLEAR、VMPTRLD、VMPTRST、VMREAD、VMWRITE、VMXON、XRSTORS 和 XSAVES,退出限定接收指令位移的值字段,如有必要,该字段将符号扩展为 64 位(在不支持 Intel 64 架构的处理器上为 32 位)。如果指令没有位移(例如,有寄存器操作数),则将零存储到退出限定中。

在支持 Intel 64 架构的处理器上,RIP 相对寻址(仅在 64 位模式下使用)是一个例外。此类寻址使指令使用的地址是位移字段与引用后续指令的 RIP 值之和。在这种情况下,退出资格加载位移场和适当的 RIP 值的总和。

在所有情况下,该字段超出指令地址大小的位都是未定义的。例如,假设 VM Exits指令信息字段(参见第 25.9.4 节和第 28.2.5 节)中的地址大小字段报告 n 位地址大小。那么指令位移的位 63: n(在不支持 Intel 64 架构的处理器上为位 31: n)未定义。

-

对于控制寄存器访问,退出限定包含有关访问的信息,其格式如表 28-3 所示。

-

对于 MOV DR,退出限定包含有关指令的信息,其格式如表 28-4 所示。

-

对于 I/O 指令,退出限定包含有关指令的信息,其格式如表 28-5 所示。

-

对于 MWAIT,退出限定包含一个值,该值指示是否进行地址范围监控

硬件已武装。退出资格设置为 0(如果地址范围监控硬件未配备)或 1(如果地址范围监控硬件配备)。

-

WBINVD 和 WBNOINVD 使用相同的基本退出原因(请参阅附录 C)。对于 WBINVD,退出资格为 0,而对于 WBNOINVD,退出资格为 1。

-

对于由于对 APIC 访问页面的线性访问或guest 物理访问而导致的 APIC 访问 VM Exits(请参阅第 30.4 节),退出限定包含有关访问的信息,并具有表 28-6 中给出的格式。

-

如果对 APIC 访问页的访问发生在飞地模式下的指令执行期间(而不是在飞地模式发生事件的传送期间),则退出资格的位 11:0 被清除。

这样的 VM Exits将退出限定的位 15:12 设置为 0000b(指令执行期间读取数据)或 0001b(指令执行期间数据写入)将位 12(区分数据读取和数据写入)设置为存储在页错误错误代码的位 1(W/R)中的访问导致了页错误,而不是 APIC 访问 VM Exits。这意味着以下内容:

-

对于由 CLFLUSH 和 CLFLUSHOPT 指令引起的 APIC 访问 VM Exits,访问类型是“指令执行期间读取数据”。

-

对于由ENTER指令引起的APIC访问VM退出,访问类型是“指令执行期间的数据写入”。

-

对于由MASKMOVQ指令或MASKMOVDQU指令引起的APIC访问VM退出,访问类型是“指令执行期间的数据写入”。

-

对于由 MONITOR 指令引起的 APIC 访问 VM Exits,访问类型是“指令执行期间读取数据”。

-

对于由于访问 DS 保存区(BTS 或 PEBS)中的线性地址直接导致的 APIC 访问 VM Exits,访问类型为“用于监视的线性访问”。

-

对于因访问 DS 保存区域(例如,访问分页结构以转换线性地址)而执行的guest 物理访问而导致的 APIC 访问 VM Exits,访问类型为“用于监视或监视的guest 物理访问”痕迹。”

-

对于当“Intel PT 使用guest 物理地址”VM 执行控制为 1 时由跟踪地址预转换 (TAPT) 导致的 APIC 访问 VM Exits,访问类型为“用于监视或跟踪的guest 物理访问”。

当且仅当它将退出资格的位 15:12 设置为 0011b(事件传递期间的线性访问)或 1010b(guest 物理事件交付期间的访问)。

有关这些指令和 APIC 访问 VM 出口的进一步讨论,请参见第 30.4.4 节。

对于因物理访问 APIC 访问页面而导致的 APIC 访问 VM Exits(请参阅第 30.4.6 节),退出资格未定义。

-

对于 EPT 违规,退出资格包含有关导致 EPT 违规的访问的信息,并具有表 28-7 中给出的格式。

如该表中所述,退出资格的格式和含义取决于“EPT 的基于模式的执行控制”VM 执行控制的设置以及处理器是否支持针对 EPT 违规的高级 VM Exits信息。

由于执行读取-修改-写入操作而发生的 EPT 违规设置位 1(数据写入)。是否也设置位 0(数据读取)是特定于实现的,并且对于给定的实现,对于不同类型的读取-修改-写入操作可能有所不同。

位 12 报告“NMI 由于 IRET 解锁”;参见第 28.2.3 节。

位 16 被设置用于与指令执行异步且不是事件传递的一部分的某些访问。其中包括 Intel PT 的跟踪地址预translation (TAPT)(请参阅第 26.5.4 节)、与具有“EPT 友好”增强功能的处理器上的 PEBS 相关的访问(请参阅第 20.9.5 节)以及作为用户一部分的访问- 中断传送(参见第 7.4.2 节)。

-

对于作为 EOI 虚拟化的一部分引起的 VM Exits(第 30.1.4 节),退出资格的位 7:0 设置为由 EOI 虚拟化消除的虚拟中断的向量。位 7 以上的位被清除。

-

对于 APIC 写入 VM Exits(第 30.4.3.3 节),退出限定的位 11:0 设置为导致 VM Exits的写访问的页偏移量。1 位 11 以上的位被清除。

-

对于由于页面修改日志满事件(第 29.3.6 节)而导致的 VM Exits,退出资格的位 12 报告“由于 IRET 导致 NMI 解锁”(请参阅第 28.2.3 节)。如果在 TAPT、EPT 友好的 PEBS 或用户中断传送期间发生 VM Exits,则设置位 16。退出资格的所有其他位均未定义。

-

对于由于 SPP 相关事件(第 29.3.4 节)而导致的 VM Exits,退出资格的位 11 指示事件类型:0 指示 SPP 配置错误,1 指示 SPP 未命中。退出资格的位 12 报告“NMI 由于 IRET 解锁”(参见第 28.2.3 节)。如果在 TAPT EPT 友好的 PEBS 或用户中断传送期间发生 VM Exits,则设置位 16。退出资格的所有其他位均未定义。

-

如果“PASID 转换”VM 执行控制,则为 ENQCMD 和 ENQCMDS 指令的执行执行 PASID 转换(请参见第 26.5.8 节)。 PASID 转换可能会失败,从而导致 VM Exits。这样的VM退出保存在以下项目中指定的退出资格:

- 对于 ENQCMD,退出资格是 IA32_PASID[19:0]。

- 对于 ENQCMDS,退出限定包含指令源操作数的低 32 位(在 PASID 转换之前已从内存中读取)。

-

对于由于指令超时而导致的 VM Exits(第 26.2 节),位 0 指示(如果设置)虚拟机的上下文无效并且不应恢复 VM。退出资格的位 12 报告“NMI 由于 IRET 解锁”(参见第 28.2.3 节)。退出资格的所有其他位均未定义。

-

-

在支持 Intel 64 架构的处理器上,如果逻辑处理器在 VM Exits之前未处于 64 位模式,则清除位 63:32。

-

如果 INVLPG 源操作数指定不可用的段,则退出限定中指定的线性地址将与 INVLPG 在未发生 VM Exits时使用的线性地址相匹配。该地址没有在体系结构上定义,并且可能是特定于实现的。

-

对于由 CLFLUSH 和 CLFLUSHOPT 指令引起的 APIC 访问 VM Exits,访问类型是“指令执行期间读取数据”。

-

对于由ENTER指令引起的APIC访问VM退出,访问类型是“指令执行期间的数据写入”。

-

对于由MASKMOVQ指令或MASKMOVDQU指令引起的APIC访问VM退出,访问类型是“指令执行期间的数据写入”。

-

对于由 MONITOR 指令引起的 APIC 访问 VM Exits,访问类型是“指令执行期间读取数据”。

-

对于由于访问 DS 保存区(BTS 或 PEBS)中的线性地址直接导致的 APIC 访问 VM Exits,访问类型为“用于监视的线性访问”。

-

对于因访问 DS 保存区域(例如,访问分页结构以转换线性地址)而执行的guest 物理访问而导致的 APIC 访问 VM Exits,访问类型为“用于监视或监视的guest 物理访问”痕迹。”

-

对于当“Intel PT 使用guest 物理地址”VM 执行控制为 1 时由跟踪地址预转换 (TAPT) 导致的 APIC 访问 VM Exits,访问类型为“用于监视或跟踪的guest 物理访问”。

当且仅当它将退出资格的位 15:12 设置为 0011b(事件传递期间的线性访问)或 1010b(guest 物理事件交付期间的访问)。

有关这些指令和 APIC 访问 VM 出口的进一步讨论,请参见第 30.4.4 节。

对于因物理访问 APIC 访问页面而导致的 APIC 访问 VM Exits(请参阅第 30.4.6 节),退出资格未定义。

-

对于 EPT 违规,退出资格包含有关导致 EPT 违规的访问的信息,并具有表 28-7 中给出的格式。

如该表中所述,退出资格的格式和含义取决于“EPT 的基于模式的执行控制”VM 执行控制的设置以及处理器是否支持针对 EPT 违规的高级 VM Exits信息。

由于执行读取-修改-写入操作而发生的 EPT 违规设置位 1(数据写入)。是否也设置位 0(数据读取)是特定于实现的,并且对于给定的实现,对于不同类型的读取-修改-写入操作可能有所不同。

位 12 报告“NMI 由于 IRET 解锁”;参见第 28.2.3 节。

位 16 被设置用于与指令执行异步且不是事件传递的一部分的某些访问。其中包括 Intel PT 的跟踪地址预translation (TAPT)(请参阅第 26.5.4 节)、与具有“EPT 友好”增强功能的处理器上的 PEBS 相关的访问(请参阅第 20.9.5 节)以及作为用户一部分的访问- 中断传送(参见第 7.4.2 节)。

-

对于作为 EOI 虚拟化的一部分引起的 VM Exits(第 30.1.4 节),退出资格的位 7:0 设置为由 EOI 虚拟化消除的虚拟中断的向量。位 7 以上的位被清除。

-

对于 APIC 写入 VM Exits(第 30.4.3.3 节),退出限定的位 11:0 设置为导致 VM Exits的写访问的页偏移量。1 位 11 以上的位被清除。

-

对于由于页面修改日志满事件(第 29.3.6 节)而导致的 VM Exits,退出资格的位 12 报告“由于 IRET 导致 NMI 解锁”(请参阅第 28.2.3 节)。如果在 TAPT、EPT 友好的 PEBS 或用户中断传送期间发生 VM Exits,则设置位 16。退出资格的所有其他位均未定义。

-

对于由于 SPP 相关事件(第 29.3.4 节)而导致的 VM Exits,退出资格的位 11 指示事件类型:0 指示 SPP 配置错误,1 指示 SPP 未命中。退出资格的位 12 报告“NMI 由于 IRET 解锁”(参见第 28.2.3 节)。如果在 TAPT EPT 友好的 PEBS 或用户中断传送期间发生 VM Exits,则设置位 16。退出资格的所有其他位均未定义。

-

如果“PASID 转换”VM 执行控制,则为 ENQCMD 和 ENQCMDS 指令的执行执行 PASID 转换(请参见第 26.5.8 节)。 PASID 转换可能会失败,从而导致 VM Exits。这样的VM退出保存在以下项目中指定的退出资格:

- 对于 ENQCMD,退出资格是 IA32_PASID[19:0]。

- 对于 ENQCMDS,退出限定包含指令源操作数的低 32 位(在 PASID 转换之前已从内存中读取)。

-

对于由于指令超时而导致的 VM Exits(第 26.2 节),位 0 指示(如果设置)虚拟机的上下文无效并且不应恢复 VM。退出资格的位 12 报告“NMI 由于 IRET 解锁”(参见第 28.2.3 节)。退出资格的所有其他位均未定义。

- 对于 ENQCMD,退出资格是 IA32_PASID[19:0]。

- 对于 ENQCMDS,退出限定包含指令源操作数的低 32 位(在 PASID 转换之前已从内存中读取)。

- guest 线性地址。对于某些VM出口,该字段接收与VM出口相关的线性地址。该字段针对不同的VM出口设置如下:

- 由于尝试使用内存操作数执行 LMSW,VM Exits。在这些情况下,该字段接收该操作数的线性地址。如果在 VM Exits之前逻辑处理器未处于 64 位模式,则清除位 63:32。

- VM 由于尝试执行相关段可用的 INS 或 OUTS 而退出(如果相关段不可用,则该值未定义)。 (ES 始终是 INS 的相关段;对于 OUTS,相关段是 DS,除非被指令前缀覆盖。)线性地址是相关段的基地址加上 (E)DI(对于 INS)或 (E)SI (对于 OUT)。如果在 VM Exits之前逻辑处理器未处于 64 位模式,则清除位 63:32。

-

VM 由于设置退出资格的位 7 的 EPT 违规而退出(参见表 28-7;这些都是 EPT 违规,除了由于执行 MOV CR 指令时尝试加载 PDPTE 导致的违规以及由于 TAPT 导致的违规) 。线性地址可以转换为其访问导致EPT违规的客户物理地址。或者,线性地址的转换可以引用其访问导致EPT违规的分页结构条目。如果在 VM Exits之前逻辑处理器未处于 64 位模式,则清除位 63:32。

如果在飞地模式下执行指令期间发生 EPT 违规(而不是在传送飞地模式中发生的事件期间),则该字段的位 11:0 被清除。

-

VM 由于 SPP 相关事件而退出。

-

如果“过早繁忙的影子堆栈”VM Exits控制为 1,如果 VM Exits导致影子堆栈过早繁忙,则某些 VM Exits(除了上面提到的那些)会保存与 VM Exits相关的线性地址(请参见第 26.4 节) .3).由于以下原因,VM Exits也是如此:EPT 配置错误、页面修改日志已满事件和指令超时。 (由于指令超时而导致的 VM Exits设置了退出资格的位 0,表明 VM 上下文无效,不会保存有效的线性地址。)

-

对于所有其他 VM 出口,该字段未定义。

-

guest 实际地址。对于由于 EPT 违规、EPT 配置错误或 SPP 相关事件而导致的 VM Exits,此字段接收导致 EPT 违规或 EPT 配置错误的guest 物理地址。对于所有其他 VM 出口,该字段未定义。

-

VM退出中断信息(格式见表25-19)。以下项目详细说明了如何为由于这些事件而导致 VM Exits建立此字段:

-

对于异常,位 7:0 接收异常向量(最多 31)。对于 NMI,位 7:0 设置为 2。对于外部中断,位 7:0 接收向量

-

位 10:8 设置为 0(外部中断)、2(不可屏蔽中断)、3(硬件异常)、5(特权软件异常)或 6(软件异常)。硬件异常包括除以下情况之外的所有异常:

-

INT1指令产生的调试异常(#DB);这些是特权软件例外。 (其他调试异常被视为硬件异常,就像在 enclave 模式下执行 INT1 引起的异常一样。)

-

断点异常(#BP;由 INT3 生成)和溢出异常(#OF;由 INTO 生成);这些是软件例外情况。 (飞地模式下发生的 #BP 被视为硬件异常。)

超出 BOUND 范围的异常(#BR;由 BOUND 生成)和由 UD0、UD1 和 UD2 生成的无效操作码异常(#UD)是硬件异常。

-

-

如果 VM Exits是由硬件异常引起的,并且该异常会在堆栈上传递错误代码,则位 11 将设置为 1。如果逻辑处理器处于实地址模式 (CR0.PE=0) 时发生 VM Exits,则该位始终为 0。2 如果位 11 设置为 1,则错误代码置于 VM Exits中断错误代码中(见下文)

-

位 12 报告“NMI 由于 IRET 解锁”;参见第 28.2.3 节。如果VM退出是由于双重故障(中断类型为硬件异常,向量为8),则该位的值未定义。

-

位 30:13 始终设置为 0。

-

位 31 始终设置为 1。

对于其他 VM Exits(包括当“退出时确认中断”VM Exits控制为 0 时由于外部中断而导致的退出),该字段被标记为无效(通过清除位 31)并且该字段的其余部分未定义。

-

VM-退出中断错误代码

-

对于在 VM Exits中断信息字段中同时设置位 31(有效)和位 11(错误代码有效)的 VM Exits,该字段接收在事件导致 VM Exits时本应推送到堆栈上的错误代码通过 IDT 正常交付。 EXT 位在此字段中的设置与正常设置时完全相同。对于在传送双重故障期间发生的异常(如果 IDT 向量信息字段指示双重故障),EXT 位设置为 1,假设 (1) 异常会正常产生错误代码(如果没有发生) (2) 错误代码使用 EXT 位(不适用于页错误,页错误使用不同的格式)。

-

对于其他VM出口,该字段的值未定义。

-

INT1指令产生的调试异常(#DB);这些是特权软件例外。 (其他调试异常被视为硬件异常,就像在 enclave 模式下执行 INT1 引起的异常一样。)

-

断点异常(#BP;由 INT3 生成)和溢出异常(#OF;由 INTO 生成);这些是软件例外情况。 (飞地模式下发生的 #BP 被视为硬件异常。)

超出 BOUND 范围的异常(#BR;由 BOUND 生成)和由 UD0、UD1 和 UD2 生成的无效操作码异常(#UD)是硬件异常。

- 如果 VM Exits是由于作为 IRET 指令执行一部分的内存访问而导致的,并且以下条件之一成立,则该位为 1:

- “虚拟 NMI”VM 执行控制为 0,并且 NMI 的阻塞(参见表 25-3)在执行 IRET 之前生效

- “虚拟 NMI”VM 执行控制为 1,并且虚拟 NMI 阻塞在 IRET 执行之前生效。

- 对于所有其他相关 VM 出口,该位为 0。

- “虚拟 NMI”VM 执行控制为 0,并且 NMI 的阻塞(参见表 25-3)在执行 IRET 之前生效

- “虚拟 NMI”VM 执行控制为 1,并且虚拟 NMI 阻塞在 IRET 执行之前生效。

- 事件传递期间发生故障并导致 VM Exits(因为与故障相关的位在异常位图中设置为 1)。

- 任务切换是通过 IDT 中的任务门调用的。仅在任务切换的初始检查通过后,才会因任务切换而发生 VM Exits(请参阅第 26.4.2 节)。

- 事件传递导致 APIC 访问 VM Exits(参见第 30.4 节)。

- 事件传递期间发生的 EPT 违规、EPT 配置错误、页面修改日志已满事件或 SPP 相关事件。

- 在用户中断通知处理期间发生的任何上述 VM Exits(参见第 7.5.2 节)。此类 VM Exits将被视为在使用向量 UINV 传递外部中断期间发生。

- 原始事件直接导致VM退出(例如,因为原始事件是不可屏蔽中断(NMI)并且“NMI退出”VM执行控制为1)。

- 原始事件导致双故障异常,导致VM直接退出

- VM Exits是由于获取事件传递调用的处理程序的第一条指令而发生的

- VM退出是由三重故障引起的。

-

IDT 向量信息(表 25-20 中给出的格式)。以下各项详细说明了如何为事件传递期间发生的 VM Exits建立此字段:

-

如果在异常传递期间发生 VM Exits,则位 7:0 接收异常向量(最多 31)。如果在传送 NMI 期间发生 VM Exits,则位 7:0 将设置为 2。如果在传送外部中断期间发生 VM Exits,则位 7:0 接收向量。

-

位 10:8 设置为指示发生 VM Exits时传递的事件类型:0(外部中断)、2(不可屏蔽中断)、3(硬件异常)、4(软件中断)、5(特权软件中断)或6(软件异常)。

硬件异常包括除以下情况之外的所有异常:

-

INT1指令产生的调试异常(#DB);这些是特权软件例外。 (其他调试异常被视为硬件异常,就像在 enclave 模式下执行 INT1 引起的异常一样。)

-

断点异常(#BP;由 INT3 生成)和溢出异常(#OF;由 INTO 生成);这些是软件例外情况。 (飞地模式下发生的 #BP 被视为硬件异常。)

超出 BOUND 范围的异常(#BR;由 BOUND 生成)和由 UD0、UD1 和 UD2 生成的无效操作码异常(#UD)是硬件异常。

-

-

如果在发送硬件异常期间发生 VM Exits(该异常可能会在堆栈上发送错误代码),则位 11 将设置为 1。如果逻辑处理器处于实地址模式 (CR0.PE=0) 时发生 VM Exits,则该位始终为 0。2 如果位 11 设置为 1,则错误代码将放置在 IDT 向量错误代码中(见下文)。

-

位 12 未定义。

-

位 30:13 始终设置为 0。

-

位 31 始终设置为 1。

对于其他 VM 出口,该字段被标记为无效(通过清除位 31)并且该字段的其余部分未定义。

-

-

IDT 向量错误代码。

- 对于在 IDT 向量信息字段中同时设置位 31(有效)和位 11(错误代码有效)的 VM 出口,该字段接收错误代码,该错误代码将由通过VM Exits时的 IDT。当正常设置时,EXT 位在此字段中设置。

- 对于其他VM出口,该字段的值未定义

-

如果在异常传递期间发生 VM Exits,则位 7:0 接收异常向量(最多 31)。如果在传送 NMI 期间发生 VM Exits,则位 7:0 将设置为 2。如果在传送外部中断期间发生 VM Exits,则位 7:0 接收向量。

-

位 10:8 设置为指示发生 VM Exits时传递的事件类型:0(外部中断)、2(不可屏蔽中断)、3(硬件异常)、4(软件中断)、5(特权软件中断)或6(软件异常)。

硬件异常包括除以下情况之外的所有异常:

-

INT1指令产生的调试异常(#DB);这些是特权软件例外。 (其他调试异常被视为硬件异常,就像在 enclave 模式下执行 INT1 引起的异常一样。)

-

断点异常(#BP;由 INT3 生成)和溢出异常(#OF;由 INTO 生成);这些是软件例外情况。 (飞地模式下发生的 #BP 被视为硬件异常。)

超出 BOUND 范围的异常(#BR;由 BOUND 生成)和由 UD0、UD1 和 UD2 生成的无效操作码异常(#UD)是硬件异常。

-

-

如果在发送硬件异常期间发生 VM Exits(该异常可能会在堆栈上发送错误代码),则位 11 将设置为 1。如果逻辑处理器处于实地址模式 (CR0.PE=0) 时发生 VM Exits,则该位始终为 0。2 如果位 11 设置为 1,则错误代码将放置在 IDT 向量错误代码中(见下文)。

-

位 12 未定义。

-

位 30:13 始终设置为 0。

-

位 31 始终设置为 1。

对于其他 VM 出口,该字段被标记为无效(通过清除位 31)并且该字段的其余部分未定义。

-

INT1指令产生的调试异常(#DB);这些是特权软件例外。 (其他调试异常被视为硬件异常,就像在 enclave 模式下执行 INT1 引起的异常一样。)

-

断点异常(#BP;由 INT3 生成)和溢出异常(#OF;由 INTO 生成);这些是软件例外情况。 (飞地模式下发生的 #BP 被视为硬件异常。)

超出 BOUND 范围的异常(#BR;由 BOUND 生成)和由 UD0、UD1 和 UD2 生成的无效操作码异常(#UD)是硬件异常。

- 对于在 IDT 向量信息字段中同时设置位 31(有效)和位 11(错误代码有效)的 VM 出口,该字段接收错误代码,该错误代码将由通过VM Exits时的 IDT。当正常设置时,EXT 位在此字段中设置。

- 对于其他VM出口,该字段的值未定义

- VM-退出指令长度。该字段用于以下情况:

- 对于由于尝试执行以下指令之一导致 VM 无条件退出(请参阅第 26.1.2 节)或基于 VM 执行控制的设置(请参阅第 26.1.3 节)而导致的类故障 VM Exits:CLTS、CPUID、 ENCLS、GETSEC、HLT、IN、INS、INVD、INVEPT、INVLPG、INVPCID、INVVPID、LGDT、LIDT、LLDT、LMSW、LOADIWKEY、LTR、MONITOR、MOV CR、MOV DR、MWAIT、OUT、OUTS、暂停、PCONFIG、 RDMSR、RDPMC、RDRAND、RDSEED、RDTSC、RDTSCP、RSM、SGDT、SIDT、SLDT、STR、TPAUSE、UMWAIT、VMCALL、VMCLEAR、VMLAUNCH、VMPTRLD、VMPTRST、VMREAD、VMRESUME、VMWRITE、VMXOFF、VMXON、WBINVD、WBNOINVD、 WRMSR、XRSTORS、XSETBV 和 XSAVES。

- 对于由于软件异常(由执行 INT3 或 INTO 生成的异常)或特权软件异常(由执行 INT1 生成的异常)导致的 VM Exits。

- 因软件中断下发、特权软件异常、软件异常等故障导致虚拟机退出。

- 由于尝试通过指令执行实现任务切换而导致 VM Exits。这些是 VM Exits,会产生指示任务切换的退出原因以及以下任一情况:

- 指示执行 CALL、IRET 或 JMP 指令的退出限定。

- 指示 IDT 中的任务门的退出资格和指示在软件中断、特权软件异常或软件异常的传递期间遇到任务门的 IDT 向量信息字段。

- 对于 APIC 访问 VM Exits以及由 EPT 违规、页面修改日志满事件以及在传送软件中断、特权软件异常或软件异常期间遇到的 SPP 相关事件引起的 VM Exits。

- 对于由于以下任一情况而导致 VMFUNC 执行失败而导致的 VM Exits:

- EAX 指示未启用的 VM 功能(VM 功能控制中 EAX 位置处的位为 0;请参见第 26.5.6.2 节)。

- EAX = 0 且 ECX ≥ 512 或 ECX 的值选择无效的暂定 EPTP 值(请参见第 26.5.6.3 节)。

- 指示执行 CALL、IRET 或 JMP 指令的退出限定。

- 指示 IDT 中的任务门的退出资格和指示在软件中断、特权软件异常或软件异常的传递期间遇到任务门的 IDT 向量信息字段。

- EAX 指示未启用的 VM 功能(VM 功能控制中 EAX 位置处的位为 0;请参见第 26.5.6.2 节)。

- EAX = 0 且 ECX ≥ 512 或 ECX 的值选择无效的暂定 EPTP 值(请参见第 26.5.6.3 节)。

-

VM-exit指令信息。对于由于尝试执行 INS、INVEPT、INVPCID、INVVPID、LIDT、LGDT、LLDT、LOADIWKEY、LTR、OUTS、RDRAND、RDSEED、SIDT、SGDT、SLDT、STR、VMCLEAR、VMPTRLD、VMPTRST、VMREAD、VMWRITE 而导致 VM ExitsVMXON、XRSTORS 或 XSAVES,该字段接收有关导致 VM Exits的指令的信息。该字段的格式取决于导致VM退出的指令的标识:

-

对于由于尝试执行 INS 或 OUTS 而导致 VM Exits,该字段的格式如表 28-8 所示

-

对于由于尝试执行 INVEPT、INVPCID 或 INVVPID 而导致 VM Exits,该字段的格式如表 28-9 所示。

-

对于由于尝试执行 LIDT、LGDT、SIDT 或 SGDT 而导致 VM Exits,该字段的格式如表 28-10 所示

-

对于由于尝试执行 LLDT、LTR、SLDT 或 STR 而导致 VM Exits,该字段的格式如表 28-11 所示。

-

对于由于尝试执行 RDRAND、RDSEED、TPAUSE 或 UMWAIT 而导致 VM Exits,该字段的格式如表 28-12 所示。

-

对于由于尝试执行 VMCLEAR、VMPTRLD、VMPTRST、VMXON、XRSTORS 或 XSAVES 导致的 VM Exits,该字段的格式如表 28-13 所示。

-

对于由于尝试执行 VMREAD 或 VMWRITE 而导致 VM Exits,该字段的格式如表 28-14 所示。

-

对于由于尝试执行 LOADIWKEY 而导致 VM Exits,该字段的格式如表 28-15 所示。

对于所有其他 VM Exits,该字段未定义,除非 VM Exits发生在 enclave 模式下,在这种情况下该字段将被清除

-

I/O RCX、I/O RSI、I/O RDI、I/O RIP。除了由于 I/O 指令退出后立即到达的系统管理中断 (SMI) 导致的 SMM VM Exits之外,这些字段未定义。参见第 32.15.2.3 节。请注意,如果 VM Exits发生在 enclave 模式下,则这些字段都会被清除。

- CR0、CR3、CR4以及IA32_SYSENTER_CS、IA32_SYSENTER_ESP和IA32_SYSENTER_EIP MSR的内容保存到相应的字段中。 IA32_SYSENTER_CS MSR 的位 63:32 不保存。在不支持 Intel 64 架构的处理器上,不会保存 IA32_SYSENTER_ESP 和 IA32_SYSENTER_EIP MSR 的位 63:32。

- 如果“保存调试控制”VM退出控制为1,则DR7和IA32_DEBUGCTL MSR的内容被保存到相应的字段中。第一个支持虚拟机扩展的处理器仅支持此控件的 1 设置,因此始终将数据保存到这些字段中。

- 如果“保存IA32_PAT”VM退出控制为1,则IA32_PAT MSR的内容被保存到相应的字段中。

- 如果“保存IA32_EFER”VM退出控制为1,则IA32_EFER MSR的内容被保存到相应的字段中。

- 如果处理器支持“加载 IA32_BNDCFGS”VM entry控制的 1 设置或“清除 IA32_BNDCFGS”VM Exits控制的 1 设置,则 IA32_BNDCFGS MSR 的内容将保存到相应的字段中。

- 如果处理器支持“加载 IA32_RTIT_CTL”VM entry控制或“清除 IA32_RTIT_CTL”VM Exits控制的 1 设置,则 IA32_RTIT_CTL MSR 的内容将保存到相应的字段中。

- 如果处理器支持“加载 CET”VM entries控制的 1 设置,则 IA32_S_CET 和 IA32_INTERRUPT_SSP_TABLE_ADDR MSR 的内容将保存到相应的字段中。在不支持 Intel 64 架构的处理器上,不会保存这些 MSR 的位 63:32。

- 如果处理器支持“加载客机 IA32_LBR_CTL”VM entry控制或“清除 IA32_LBR_CTL”VM Exits控制的 1 设置,则 IA32_LBR_CTL MSR 的内容将保存到相应的字段中。

- 如果处理器支持“加载 PKRS”VM entry控制的 1 设置,则 IA32_PKRS MSR 的内容将保存到相应字段中。

- 如果处理器支持用户中断,则每个 VM 出口都会将 UINV 保存到 VMCS 中的guest UINV 字段中(该字段的位 15:8 被清除)。

- 如果“保存 IA32_PERF_GLOBAL_CTL”VM Exits控制为 1,则 IA32_PERF_GLOBAL_CTL MSR 的内容将保存到相应字段中。

- 除SMM虚拟机退出外,所有虚拟机退出后,SMBASE字段的值均未定义。参见第 32.15.2 节。

- 如果寄存器不可用,则保存到以下字段中的值是未定义的: (1) 基地址; (2) 分段限制; (3)访问权限字段中的比特7:0和比特15:12。以下例外情况适用:

- CS。

- 保存基地址和段限制字段。

- L、D 和G 位保存在访问权限字段中。

- SS。

- DPL 保存在访问权限字段中。

- 在支持 Intel 64 架构的处理器上,为基地址保存的值的第 63:32 位始终为零。

- DS 和 ES。在支持 Intel 64 架构的处理器上,为基地址保存的值的第 63:32 位始终为零。

- FS 和 GS。基地址字段被保存。

- LDTR。为基地址保存的值始终是规范的。

- CS。

- 如果寄存器不是不可用,则保存到以下字段中的值是 VM Exits之前寄存器中的值: (1) 基地址; (2) 分段限制; (3) 访问权限中的位 7:0 和位 15:12。

- 访问权限字段中的位 31:17 和 11:8 始终被清除。当且仅当该段不可用时,位 16 才设置为 1。

- CS。

- 保存基地址和段限制字段。

- L、D 和G 位保存在访问权限字段中。

- SS。

- DPL 保存在访问权限字段中。

- 在支持 Intel 64 架构的处理器上,为基地址保存的值的第 63:32 位始终为零。

- DS 和 ES。在支持 Intel 64 架构的处理器上,为基地址保存的值的第 63:32 位始终为零。

- FS 和 GS。基地址字段被保存。

- LDTR。为基地址保存的值始终是规范的。

- 保存基地址和段限制字段。

- L、D 和G 位保存在访问权限字段中。

- DPL 保存在访问权限字段中。

- 在支持 Intel 64 架构的处理器上,为基地址保存的值的第 63:32 位始终为零。

- RIP字段中保存的值由VM退出的性质和原因决定:

- — 如果 VM Exits发生在 enclave 模式下,则保存的值是中断的 enclave 线程的 AEP(其余项不适用)。

- 如果由于尝试执行导致 VM 无条件退出的指令或已配置为通过 VM 执行控件导致 VM Exits而导致 VM Exits,则保存的值将引用该指令。

- 如果 VM Exits是由 INIT 信号、启动 IPI (SIPI) 或系统管理中断 (SMI) 的发生引起的,则保存的值是事件发生之前 RIP 中的值。

- 如果由于“中断窗口退出”VM 执行控制或“NMI 窗口退出”VM 执行控制设置为 1 而导致 VM Exits,则保存的值将是寄存器中的值未发生 VM Exits。

- 如果VM退出是由于外部中断、不可屏蔽中断(NMI)或硬件异常(如第28.2.2节中定义)引起的,则保存的值是本应保存的返回指针(或者在堆栈上)事件通过陷阱或中断门传递,1 或进入旧任务状态段(如果事件通过任务门传递)。

- 如果VM退出是由于三重故障,则保存的值是本来应该保存的返回指针(如果事件通过陷阱或中断门传递到堆栈上,或者保存到旧任务状态段中)通过任务门传递的事件)在传递双重错误时未遇到导致三重错误的嵌套异常。

- 如果 VM Exits是由于软件异常(由于执行 INT3 或 INTO)或特权软件异常(由于执行 INT1)导致,则保存的值将引用导致该异常的 INT3、INTO 或 INT1 指令。

- 假设VM退出是由于执行CALL、IRET或JMP或执行软件中断(INT n)、软件异常(由于执行INT3或INTO)或特权软件引起的任务切换在 IDT 中遇到任务门的异常(由于 INT1 的执行)。保存的值引用导致任务切换的指令(CALL、IRET、JMP、INT n、INT3、INTO、INT1)。

- 如果 VM Exits是由于执行到 CR8 或 WRMSR 的 MOV 导致 VTPR(参见第 30.1.1 节)的位 7:4 的值降低到低于 TPR 阈值 VM 执行控制字段(参见第 30.1.2 节) ,保存的值引用 MOV 到 CR8 或 WRMSR 之后的指令。

- 如果 VM Exits是由作为指令执行一部分的 APIC 访问导致的 APIC 写入仿真(请参阅第 30.4.3.2 节)引起的,则保存的值将引用其执行导致 APIC 写入仿真的指令后面的指令。

- RSP寄存器的内容被保存到RSP字段中。

- 除恢复标志(RF;位 16)外,RFLAGS 寄存器的内容均保存到 RFLAGS 字段中。 RFLAGS.RF保存如下:

- 如果VM退出发生在enclave模式下,则保存的值为0(其余项不适用)

- 如果 VM Exits是由通常通过 IDT 传递的事件直接引起的,则保存的值将出现在保存的 RFLAGS 映像中(如果事件通过陷阱传递,则保存在堆栈上的值)如果事件是通过任务门传递的,则进入旧任务状态段(如果事件是通过 IDT 传递的)。请参阅下文了解由于 IDT 中的任务门引起的任务切换而导致的 VM Exits。

- 如果VM退出是由三重故障引起的,则保存的值是逻辑处理器在三重故障使逻辑处理器进入关闭状态时RFLAGS寄存器中的RF中的值。

- 如果VM退出是由任务切换引起的(包括由IDT中的任务门引起的),则保存的值是在旧任务状态段(TSS)的RFLAGS映像中保存的值切换正常完成,无异常。

- 如果 VM Exits是由于尝试执行无条件导致 VM Exits的指令或配置为与 VM 执行控制相关的指令而导致的,则保存的值为 0。

- 对于 APIC 访问 VM Exits以及由 EPT 违规、EPT 配置错误、页面修改日志满事件或 SPP 相关事件引起的 VM Exits,保存的值取决于通过 IDT 传递事件期间是否发生 VM Exits:

- 如果 VM 出口为 IDT 向量信息字段的位 31 存储 0(因为在通过 IDT 传递事件期间未发生 VM 出口;请参阅第 28.2.4 节),则保存的值为 1。

- 如果 VM 出口为 IDT 向量信息字段的位 31 存储 1(因为 VM 出口确实在通过 IDT 传递事件期间发生),则保存的值是发生该事件时将出现在保存的 RFLAGS 映像中的值通过 IDT 交付(见上文)。

- 对于所有其他 VM Exits,保存的值是 VM Exits发生之前 RFLAGS.RF 的值。

- 如果处理器支持“加载CET”VM入口控制的1设置,则SSP寄存器的内容被保存到SSP字段中。

- — 如果 VM Exits发生在 enclave 模式下,则保存的值是中断的 enclave 线程的 AEP(其余项不适用)。

- 如果由于尝试执行导致 VM 无条件退出的指令或已配置为通过 VM 执行控件导致 VM Exits而导致 VM Exits,则保存的值将引用该指令。

- 如果 VM Exits是由 INIT 信号、启动 IPI (SIPI) 或系统管理中断 (SMI) 的发生引起的,则保存的值是事件发生之前 RIP 中的值。

- 如果由于“中断窗口退出”VM 执行控制或“NMI 窗口退出”VM 执行控制设置为 1 而导致 VM Exits,则保存的值将是寄存器中的值未发生 VM Exits。

- 如果VM退出是由于外部中断、不可屏蔽中断(NMI)或硬件异常(如第28.2.2节中定义)引起的,则保存的值是本应保存的返回指针(或者在堆栈上)事件通过陷阱或中断门传递,1 或进入旧任务状态段(如果事件通过任务门传递)。

- 如果VM退出是由于三重故障,则保存的值是本来应该保存的返回指针(如果事件通过陷阱或中断门传递到堆栈上,或者保存到旧任务状态段中)通过任务门传递的事件)在传递双重错误时未遇到导致三重错误的嵌套异常。

- 如果 VM Exits是由于软件异常(由于执行 INT3 或 INTO)或特权软件异常(由于执行 INT1)导致,则保存的值将引用导致该异常的 INT3、INTO 或 INT1 指令。

- 假设VM退出是由于执行CALL、IRET或JMP或执行软件中断(INT n)、软件异常(由于执行INT3或INTO)或特权软件引起的任务切换在 IDT 中遇到任务门的异常(由于 INT1 的执行)。保存的值引用导致任务切换的指令(CALL、IRET、JMP、INT n、INT3、INTO、INT1)。

- 如果 VM Exits是由于执行到 CR8 或 WRMSR 的 MOV 导致 VTPR(参见第 30.1.1 节)的位 7:4 的值降低到低于 TPR 阈值 VM 执行控制字段(参见第 30.1.2 节) ,保存的值引用 MOV 到 CR8 或 WRMSR 之后的指令。

- 如果 VM Exits是由作为指令执行一部分的 APIC 访问导致的 APIC 写入仿真(请参阅第 30.4.3.2 节)引起的,则保存的值将引用其执行导致 APIC 写入仿真的指令后面的指令。

- 如果VM退出发生在enclave模式下,则保存的值为0(其余项不适用)

- 如果 VM Exits是由通常通过 IDT 传递的事件直接引起的,则保存的值将出现在保存的 RFLAGS 映像中(如果事件通过陷阱传递,则保存在堆栈上的值)如果事件是通过任务门传递的,则进入旧任务状态段(如果事件是通过 IDT 传递的)。请参阅下文了解由于 IDT 中的任务门引起的任务切换而导致的 VM Exits。

- 如果VM退出是由三重故障引起的,则保存的值是逻辑处理器在三重故障使逻辑处理器进入关闭状态时RFLAGS寄存器中的RF中的值。

- 如果VM退出是由任务切换引起的(包括由IDT中的任务门引起的),则保存的值是在旧任务状态段(TSS)的RFLAGS映像中保存的值切换正常完成,无异常。

- 如果 VM Exits是由于尝试执行无条件导致 VM Exits的指令或配置为与 VM 执行控制相关的指令而导致的,则保存的值为 0。

- 对于 APIC 访问 VM Exits以及由 EPT 违规、EPT 配置错误、页面修改日志满事件或 SPP 相关事件引起的 VM Exits,保存的值取决于通过 IDT 传递事件期间是否发生 VM Exits:

- 如果 VM 出口为 IDT 向量信息字段的位 31 存储 0(因为在通过 IDT 传递事件期间未发生 VM 出口;请参阅第 28.2.4 节),则保存的值为 1。

- 如果 VM 出口为 IDT 向量信息字段的位 31 存储 1(因为 VM 出口确实在通过 IDT 传递事件期间发生),则保存的值是发生该事件时将出现在保存的 RFLAGS 映像中的值通过 IDT 交付(见上文)。

- 对于所有其他 VM Exits,保存的值是 VM Exits发生之前 RFLAGS.RF 的值。

- 如果 VM 出口为 IDT 向量信息字段的位 31 存储 0(因为在通过 IDT 传递事件期间未发生 VM 出口;请参阅第 28.2.4 节),则保存的值为 1。

- 如果 VM 出口为 IDT 向量信息字段的位 31 存储 1(因为 VM 出口确实在通过 IDT 传递事件期间发生),则保存的值是发生该事件时将出现在保存的 RFLAGS 映像中的值通过 IDT 交付(见上文)。

-

活动状态字段在 VM Exits之前与逻辑处理器的活动状态一起保存。1 有关导致 VM Exits的事件如何影响活动状态的详细信息,请参见第 28.1 节。如果VM退出发生在用户中断通知处理期间(参见第7.5.2节),并且逻辑处理器在用户中断通知处理之后进入HLT状态,则保存的活动状态为“HLT”。

-

保存可中断状态字段以反映VM退出之前逻辑处理器的可中断性

- 有关导致 VM Exits的事件如何影响此状态的详细信息,请参阅第 28.1 节。

- VM Exits系统管理模式 (SMM) 之外时,将位 2(由 SMI 阻止)保存为 0,无论 VM Exits之前此类阻止的状态如何。

- 如果“虚拟 NMI”VM 执行控制为 1,则对位 3(NMI 阻塞)进行特殊处理。在这种情况下,为此字段保存的值并不指示 NMI 阻塞,而是指示虚拟 NMI 阻塞的状态。

- 如果逻辑处理器处于 enclave 模式时发生 VM Exits,则位 4(enclave 中断)设置为 1。

此类VM退出包括由中断、不可屏蔽中断、系统管理中断、INIT信号和飞地模式中发生的异常以及在飞地模式中发生的此类事件的传递期间遇到的异常引起的退出。

与 VM entries注入的事件的传递相关的 VM Exits使该位保持不变。

-

对于所有 VM Exits,挂起的调试异常字段都会保存为清除状态,以下情况除外:

- 由 INIT 信号、机器检查异常或系统管理中断 (SMI) 引起的 VM Exits。

- VM Exits,其基本退出原因为“TPR 低于阈值”、2“虚拟化 EOI”、“APIC 写入”、“监视器陷阱标志”或“检测到总线锁定”。

- 由于跟踪地址预转换(TAPT;请参阅第 26.5.4 节)或由于具有“EPT 友好”增强功能的处理器上与 PEBS 相关的访问(请参阅第 20.9.5 节)而导致 VM Exits。此类 VM Exits可能具有基本退出原因“APIC 访问”、“EPT 违规”、“EPT 配置错误”、“页面修改日志已满”或“SPP 相关事件”。当由于 TAPT 或 PEBS 导致时,这些 VM Exits(由于 EPT 错误配置导致的退出除外)设置退出限定的位 16,指示它们与指令执行异步,而不是事件传递的一部分。

- VM Exits不是由调试异常引起的,而是在 MOV-SS 阻止调试异常时发生。

对于不清除该字段的 VM Exits,保存的值确定如下:

-

如果位 3:0 中的每一位对应于匹配的断点,则可以对其进行设置。即使 DR7 中未启用相应的断点,情况也可能如此。

-

假设 VM Exits是由于 INIT 信号、机器检查异常或 SMI 导致的;或者 VM Exits具有基本退出原因“TPR 低于阈值”或“监视器陷阱标志”。在这种情况下,保存的值设置与 VM Exits时未决的任何调试异常的原因相对应的位。

如果 VM Exits在 VM entry后立即发生,则保存的值可能与 VM entry时加载的值匹配(请参阅第 27.7.3 节)。否则,适用以下条款:

-

在以下任一情况下,位 12(启用断点)设置为 1:

- DR7 中是否启用了至少一个匹配的数据或 I/O 断点。

- 如果在 VM entry时设置它,则会导致存在有效的待处理调试异常(请参阅第 27.7.3 节),并且在这些异常传递或丢失之前发生 VM Exits。

- 如果在 VM Exits之前立即执行 XBEGIN 指令,并且已启用 RTM 事务区域的高级调试(请参阅《英特尔® 64 和 IA-32 架构软件开发人员手册》卷的第 16.3.7 节“启用 RTM 的调试器支持”) 1)。 (这不适用于具有基本退出原因“监视器陷阱标志”的 VM Exits。)

- 如果在 CPL > 0 且操作系统总线锁定检测已启用时断言总线锁定

在其他情况下,位 12 被清除为 0。

-

如果在以下任一情况下 RFLAGS.TF = 1,则设置位 14 (BS):

- IA32_DEBUGCTL.BTF = 0,挂起的调试异常的原因是执行单个指令。

- IA32_DEBUGCTL.BTF = 1 并且挂起的调试异常的原因是已采用的分支。

-

如果在已启用 RTM 事务区域的高级调试的情况下在 RTM 区域内发生调试异常 (#DB) 或断点异常 (#BP),则设置位 16 (RTM)。 (这不适用于具有基本退出原因“监视器陷阱标志”的 VM Exits。)

-

-

假设 VM Exits是由于其他原因(但不是调试异常)并且在 MOV SS 阻止调试异常时发生。在这种情况下,保存的值设置与 VM Exits时未决的任何调试异常的原因相对应的位。如果VM退出发生在VM进入之后(在VMX非root操作中没有执行任何指令),则保存的值可能与VM进入时加载的值匹配(参见第27.7.3节)。否则,适用以下条款:

- 如果 DR7 中启用了至少一个匹配的数据或 I/O 断点,则位 12(启用的断点)将设置为 1。如果在 VM entry时设置了位 12,则也会设置位 12,从而导致存在有效的待处理调试异常(请参阅第 27.7.3 节),并且在这些异常传递或丢失之前发生 VM Exits。在其他情况下,位 12 被清除为 0。

- 位 14 (BS) 的设置是特定于实现的。但是,如果 RFLAGS.TF = 0 或 IA32_DEBUGCTL.BTF = 1,则不会设置该值。

-

该字段中的保留位被清除。

-

如果“保存VMX抢占定时器值”VM退出控制为1,则定时器的值被保存到VMX抢占定时器值字段中。这是在 VM entries上从该字段加载的值,随后递减(参见第 26.5.1 节)。由于定时器到期而退出的 VM 保存值 0。如果在 VM Exits期间定时器到期,其他 VM Exits也可能保存值 0。 (如果“保存VMX抢占计时器值”VM退出控制为0,则VM退出不会修改VMX抢占计时器值字段的值。)

-

如果逻辑处理器支持“启用 EPT”VM 执行控制的 1 设置,则值将保存到四 (4) 个 PDPTE 字段中,如下所示:

- 如果“启用 EPT”VM 执行控制为 1 并且逻辑处理器在 VM Exits时使用 PAE 分页,则保存当前使用的 PDPTE 值:

- 保存到每个字段的位 11:9 中的值未定义。

- 如果保存到某一字段中的值的位 0(存在)已清除,则保存到该字段的位 63:1 中的值未定义。该值不需要对应于 VM entries加载的值或可能已在 VMX non-root operation中加载的任何值。

- 如果保存到字段之一的值设置了位 0(存在),则保存到该字段的位 63:12 的值是客户物理地址。

- 如果“启用 EPT”VM 执行控制为 0 或逻辑处理器在 VM Exits时未使用 PAE 分页,则保存的值未定义。

- 如果“启用 EPT”VM 执行控制为 1 并且逻辑处理器在 VM Exits时使用 PAE 分页,则保存当前使用的 PDPTE 值:

- 有关导致 VM Exits的事件如何影响此状态的详细信息,请参阅第 28.1 节。

- VM Exits系统管理模式 (SMM) 之外时,将位 2(由 SMI 阻止)保存为 0,无论 VM Exits之前此类阻止的状态如何。

- 如果“虚拟 NMI”VM 执行控制为 1,则对位 3(NMI 阻塞)进行特殊处理。在这种情况下,为此字段保存的值并不指示 NMI 阻塞,而是指示虚拟 NMI 阻塞的状态。

- 如果逻辑处理器处于 enclave 模式时发生 VM Exits,则位 4(enclave 中断)设置为 1。

- 由 INIT 信号、机器检查异常或系统管理中断 (SMI) 引起的 VM Exits。

- VM Exits,其基本退出原因为“TPR 低于阈值”、2“虚拟化 EOI”、“APIC 写入”、“监视器陷阱标志”或“检测到总线锁定”。

- 由于跟踪地址预转换(TAPT;请参阅第 26.5.4 节)或由于具有“EPT 友好”增强功能的处理器上与 PEBS 相关的访问(请参阅第 20.9.5 节)而导致 VM Exits。此类 VM Exits可能具有基本退出原因“APIC 访问”、“EPT 违规”、“EPT 配置错误”、“页面修改日志已满”或“SPP 相关事件”。当由于 TAPT 或 PEBS 导致时,这些 VM Exits(由于 EPT 错误配置导致的退出除外)设置退出限定的位 16,指示它们与指令执行异步,而不是事件传递的一部分。

- VM Exits不是由调试异常引起的,而是在 MOV-SS 阻止调试异常时发生。

-

如果位 3:0 中的每一位对应于匹配的断点,则可以对其进行设置。即使 DR7 中未启用相应的断点,情况也可能如此。

-

假设 VM Exits是由于 INIT 信号、机器检查异常或 SMI 导致的;或者 VM Exits具有基本退出原因“TPR 低于阈值”或“监视器陷阱标志”。在这种情况下,保存的值设置与 VM Exits时未决的任何调试异常的原因相对应的位。

如果 VM Exits在 VM entry后立即发生,则保存的值可能与 VM entry时加载的值匹配(请参阅第 27.7.3 节)。否则,适用以下条款:

-

在以下任一情况下,位 12(启用断点)设置为 1:

- DR7 中是否启用了至少一个匹配的数据或 I/O 断点。

- 如果在 VM entry时设置它,则会导致存在有效的待处理调试异常(请参阅第 27.7.3 节),并且在这些异常传递或丢失之前发生 VM Exits。

- 如果在 VM Exits之前立即执行 XBEGIN 指令,并且已启用 RTM 事务区域的高级调试(请参阅《英特尔® 64 和 IA-32 架构软件开发人员手册》卷的第 16.3.7 节“启用 RTM 的调试器支持”) 1)。 (这不适用于具有基本退出原因“监视器陷阱标志”的 VM Exits。)

- 如果在 CPL > 0 且操作系统总线锁定检测已启用时断言总线锁定

在其他情况下,位 12 被清除为 0。

-

如果在以下任一情况下 RFLAGS.TF = 1,则设置位 14 (BS):

- IA32_DEBUGCTL.BTF = 0,挂起的调试异常的原因是执行单个指令。

- IA32_DEBUGCTL.BTF = 1 并且挂起的调试异常的原因是已采用的分支。

-

如果在已启用 RTM 事务区域的高级调试的情况下在 RTM 区域内发生调试异常 (#DB) 或断点异常 (#BP),则设置位 16 (RTM)。 (这不适用于具有基本退出原因“监视器陷阱标志”的 VM Exits。)

-

-

假设 VM Exits是由于其他原因(但不是调试异常)并且在 MOV SS 阻止调试异常时发生。在这种情况下,保存的值设置与 VM Exits时未决的任何调试异常的原因相对应的位。如果VM退出发生在VM进入之后(在VMX非root操作中没有执行任何指令),则保存的值可能与VM进入时加载的值匹配(参见第27.7.3节)。否则,适用以下条款:

- 如果 DR7 中启用了至少一个匹配的数据或 I/O 断点,则位 12(启用的断点)将设置为 1。如果在 VM entry时设置了位 12,则也会设置位 12,从而导致存在有效的待处理调试异常(请参阅第 27.7.3 节),并且在这些异常传递或丢失之前发生 VM Exits。在其他情况下,位 12 被清除为 0。

- 位 14 (BS) 的设置是特定于实现的。但是,如果 RFLAGS.TF = 0 或 IA32_DEBUGCTL.BTF = 1,则不会设置该值。

-

该字段中的保留位被清除。

-

在以下任一情况下,位 12(启用断点)设置为 1:

- DR7 中是否启用了至少一个匹配的数据或 I/O 断点。

- 如果在 VM entry时设置它,则会导致存在有效的待处理调试异常(请参阅第 27.7.3 节),并且在这些异常传递或丢失之前发生 VM Exits。

- 如果在 VM Exits之前立即执行 XBEGIN 指令,并且已启用 RTM 事务区域的高级调试(请参阅《英特尔® 64 和 IA-32 架构软件开发人员手册》卷的第 16.3.7 节“启用 RTM 的调试器支持”) 1)。 (这不适用于具有基本退出原因“监视器陷阱标志”的 VM Exits。)

- 如果在 CPL > 0 且操作系统总线锁定检测已启用时断言总线锁定

在其他情况下,位 12 被清除为 0。

-

如果在以下任一情况下 RFLAGS.TF = 1,则设置位 14 (BS):

- IA32_DEBUGCTL.BTF = 0,挂起的调试异常的原因是执行单个指令。

- IA32_DEBUGCTL.BTF = 1 并且挂起的调试异常的原因是已采用的分支。

-

如果在已启用 RTM 事务区域的高级调试的情况下在 RTM 区域内发生调试异常 (#DB) 或断点异常 (#BP),则设置位 16 (RTM)。 (这不适用于具有基本退出原因“监视器陷阱标志”的 VM Exits。)

- DR7 中是否启用了至少一个匹配的数据或 I/O 断点。

- 如果在 VM entry时设置它,则会导致存在有效的待处理调试异常(请参阅第 27.7.3 节),并且在这些异常传递或丢失之前发生 VM Exits。

- 如果在 VM Exits之前立即执行 XBEGIN 指令,并且已启用 RTM 事务区域的高级调试(请参阅《英特尔® 64 和 IA-32 架构软件开发人员手册》卷的第 16.3.7 节“启用 RTM 的调试器支持”) 1)。 (这不适用于具有基本退出原因“监视器陷阱标志”的 VM Exits。)

- 如果在 CPL > 0 且操作系统总线锁定检测已启用时断言总线锁定

- IA32_DEBUGCTL.BTF = 0,挂起的调试异常的原因是执行单个指令。

- IA32_DEBUGCTL.BTF = 1 并且挂起的调试异常的原因是已采用的分支。

- 如果 DR7 中启用了至少一个匹配的数据或 I/O 断点,则位 12(启用的断点)将设置为 1。如果在 VM entry时设置了位 12,则也会设置位 12,从而导致存在有效的待处理调试异常(请参阅第 27.7.3 节),并且在这些异常传递或丢失之前发生 VM Exits。在其他情况下,位 12 被清除为 0。

- 位 14 (BS) 的设置是特定于实现的。但是,如果 RFLAGS.TF = 0 或 IA32_DEBUGCTL.BTF = 1,则不会设置该值。

- 如果“启用 EPT”VM 执行控制为 1 并且逻辑处理器在 VM Exits时使用 PAE 分页,则保存当前使用的 PDPTE 值:

- 保存到每个字段的位 11:9 中的值未定义。

- 如果保存到某一字段中的值的位 0(存在)已清除,则保存到该字段的位 63:1 中的值未定义。该值不需要对应于 VM entries加载的值或可能已在 VMX non-root operation中加载的任何值。

- 如果保存到字段之一的值设置了位 0(存在),则保存到该字段的位 63:12 的值是客户物理地址。

- 如果“启用 EPT”VM 执行控制为 0 或逻辑处理器在 VM Exits时未使用 PAE 分页,则保存的值未定义。

- 保存到每个字段的位 11:9 中的值未定义。

- 如果保存到某一字段中的值的位 0(存在)已清除,则保存到该字段的位 63:1 中的值未定义。该值不需要对应于 VM entries加载的值或可能已在 VMX non-root operation中加载的任何值。

- 如果保存到字段之一的值设置了位 0(存在),则保存到该字段的位 63:12 的值是客户物理地址。

- 位 31:8 的值为 000008H,这意味着当本地 APIC 处于 x2APIC 模式时,索引 MSR 允许访问 APIC 寄存器。

- 位 31:0 的值指示只能在系统管理模式 (SMM) 下读取的 MSR,并且 VM Exits不会以 SMM 结束。 (IA32_SMBASE是一个只能在SMM中读取的MSR。)

- 位 31:0 的值表示由于特定于模型的原因,无法在 VM Exits时保存 MSR。处理器可能会阻止某些 MSR(基于位 31:0 的值)存储在 VM 出口上,即使 RDMSR 可以正常读取它们。此类特定于模型的行为记录在《英特尔® 64 和 IA-32 架构软件开发人员手册》第 4 卷的第 2 章“特定于模型的寄存器 (MSR)”中。

- 该条目的第 63:32 位不全为 0。

- 如果在 CPL = 0 的情况下通过 RDMSR 执行,尝试读取由位 31:0 索引的 MSR 将导致一般保护异常。

- 某些状态是从host状态区域的内容加载或以其他方式确定的

- 某些状态由 VM Exits控件确定。

- 每个虚拟机退出时都会以相同的方式建立某些状态。

- 页目录指针是根据某些控制寄存器的值加载的。

-

CR0、CR3 和 CR4 分别从 CR0 字段、CR3 字段和 CR4 字段加载,但以下情况除外:

- 以下位未修改:

- 对于 CR0、ET、CD、NW;位 63:32(在支持 Intel 64 架构的处理器上)、28:19、17 和 15:6;以及 VMX 操作中固定的任何位(参见第 24.8 节)。

- 对于 CR3,位 63:52 和位范围 51:32 超出处理器的物理地址宽度(它们被清除为 0)。2(此项仅适用于支持 Intel 64 架构的处理器。)

- 对于 CR4,VMX 操作中固定的任何位(参见第 24.8 节)。

- 如果“host地址空间大小”VM Exits控制为 1,则 CR4.PAE 设置为 1。

- 如果“host地址空间大小”VM Exits控制为 0,则 CR4.PCIDE 设置为 0。

- 以下位未修改:

-

DR7 设置为 400H。

-

如果“清除 UINV”VM Exits控制为 1,VM Exits将清除 UINV

-

以下MSR的建立如下:

-

IA32_DEBUGCTL MSR 被清除为 00000000_00000000H

-

IA32_SYSENTER_CS MSR 是从 IA32_SYSENTER_CS 字段加载的。由于该字段只有 32 位,因此 MSR 的位 63:32 被清除为 0。

-

IA32_SYSENTER_ESP 和 IA32_SYSENTER_EIP MSR 分别从 IA32_SYSENTER_ESP 和 IA32_SYSENTER_EIP 字段加载。

如果处理器不支持Intel 64架构,这些字段只有32位; MSR 的位 63:32 被清除为 0。

如果处理器支持 N < 64 个线性地址位的 Intel 64 架构,则 63:N 位中的每一位都将设置为位 N–1 的值。

-

以下步骤在支持 Intel 64 架构的处理器上执行:

- MSR FS.base 和 GS.base 分别从 FS 和 GS 的基地址字段加载(参见第 28.5.2 节)。

- IA32_EFER MSR 中的 LMA 和 LME 位均加载了“host地址空间大小”VM Exits控制的设置。

-

如果“加载 IA32_PERF_GLOBAL_CTRL”VM Exits控制为 1,则从 IA32_PERF_GLOBAL_CTRL 字段加载 IA32_PERF_GLOBAL_CTRL MSR。该 MSR 中保留的位以其保留值进行维护。

-

如果“加载 IA32_PAT”VM Exits控制为 1,则从 IA32_PAT 字段加载 IA32_PAT MSR。该 MSR 中保留的位以其保留值进行维护。

-

如果“加载 IA32_EFER”VM Exits控制为 1,则从 IA32_EFER 字段加载 IA32_EFER MSR。该 MSR 中保留的位以其保留值进行维护。

-

如果“清除 IA32_BNDCFGS”VM Exits控制为 1,则 IA32_BNDCFGS MSR 被清除为 00000000_00000000H;否则不予修改。

-

如果“清除 IA32_RTIT_CTL”VM Exits控制为 1,则 IA32_RTIT_CTL MSR 被清除为 00000000_00000000H;否则不予修改。

-

如果“加载 CET”VM Exits控制为 1,则分别从 IA32_S_CET 和 IA32_INTERRUPT_SSP_TABLE_ADDR 字段加载 IA32_S_CET 和 IA32_INTERRUPT_SSP_TABLE_ADDR MSR。

如果处理器不支持Intel 64架构,这些字段只有32位; MSR 的位 63:32 被清除为 0。

如果处理器支持 N < 64 个线性地址位的 Intel 64 架构,则 63:N 位中的每一位都将设置为位 N–1 的值。

-

如果“加载 PKRS”VM Exits控制为 1,则从 IA32_PKRS 字段加载 IA32_PKRS MSR。该 MSR 的位 63:32 保持为零。

-

- 以下位未修改:

- 对于 CR0、ET、CD、NW;位 63:32(在支持 Intel 64 架构的处理器上)、28:19、17 和 15:6;以及 VMX 操作中固定的任何位(参见第 24.8 节)。

- 对于 CR3,位 63:52 和位范围 51:32 超出处理器的物理地址宽度(它们被清除为 0)。2(此项仅适用于支持 Intel 64 架构的处理器。)

- 对于 CR4,VMX 操作中固定的任何位(参见第 24.8 节)。

- 如果“host地址空间大小”VM Exits控制为 1,则 CR4.PAE 设置为 1。

- 如果“host地址空间大小”VM Exits控制为 0,则 CR4.PCIDE 设置为 0。

- 对于 CR0、ET、CD、NW;位 63:32(在支持 Intel 64 架构的处理器上)、28:19、17 和 15:6;以及 VMX 操作中固定的任何位(参见第 24.8 节)。

- 对于 CR3,位 63:52 和位范围 51:32 超出处理器的物理地址宽度(它们被清除为 0)。2(此项仅适用于支持 Intel 64 架构的处理器。)

- 对于 CR4,VMX 操作中固定的任何位(参见第 24.8 节)。

-

IA32_DEBUGCTL MSR 被清除为 00000000_00000000H

-

IA32_SYSENTER_CS MSR 是从 IA32_SYSENTER_CS 字段加载的。由于该字段只有 32 位,因此 MSR 的位 63:32 被清除为 0。

-

IA32_SYSENTER_ESP 和 IA32_SYSENTER_EIP MSR 分别从 IA32_SYSENTER_ESP 和 IA32_SYSENTER_EIP 字段加载。

如果处理器不支持Intel 64架构,这些字段只有32位; MSR 的位 63:32 被清除为 0。

如果处理器支持 N < 64 个线性地址位的 Intel 64 架构,则 63:N 位中的每一位都将设置为位 N–1 的值。

-

以下步骤在支持 Intel 64 架构的处理器上执行:

- MSR FS.base 和 GS.base 分别从 FS 和 GS 的基地址字段加载(参见第 28.5.2 节)。

- IA32_EFER MSR 中的 LMA 和 LME 位均加载了“host地址空间大小”VM Exits控制的设置。

-

如果“加载 IA32_PERF_GLOBAL_CTRL”VM Exits控制为 1,则从 IA32_PERF_GLOBAL_CTRL 字段加载 IA32_PERF_GLOBAL_CTRL MSR。该 MSR 中保留的位以其保留值进行维护。

-

如果“加载 IA32_PAT”VM Exits控制为 1,则从 IA32_PAT 字段加载 IA32_PAT MSR。该 MSR 中保留的位以其保留值进行维护。

-

如果“加载 IA32_EFER”VM Exits控制为 1,则从 IA32_EFER 字段加载 IA32_EFER MSR。该 MSR 中保留的位以其保留值进行维护。

-

如果“清除 IA32_BNDCFGS”VM Exits控制为 1,则 IA32_BNDCFGS MSR 被清除为 00000000_00000000H;否则不予修改。

-

如果“清除 IA32_RTIT_CTL”VM Exits控制为 1,则 IA32_RTIT_CTL MSR 被清除为 00000000_00000000H;否则不予修改。

-

如果“加载 CET”VM Exits控制为 1,则分别从 IA32_S_CET 和 IA32_INTERRUPT_SSP_TABLE_ADDR 字段加载 IA32_S_CET 和 IA32_INTERRUPT_SSP_TABLE_ADDR MSR。

如果处理器不支持Intel 64架构,这些字段只有32位; MSR 的位 63:32 被清除为 0。

如果处理器支持 N < 64 个线性地址位的 Intel 64 架构,则 63:N 位中的每一位都将设置为位 N–1 的值。

-

如果“加载 PKRS”VM Exits控制为 1,则从 IA32_PKRS 字段加载 IA32_PKRS MSR。该 MSR 的位 63:32 保持为零。

- MSR FS.base 和 GS.base 分别从 FS 和 GS 的基地址字段加载(参见第 28.5.2 节)。

- IA32_EFER MSR 中的 LMA 和 LME 位均加载了“host地址空间大小”VM Exits控制的设置。

-

选择器是从选择器字段加载的。如果其选择器加载为零,则该段不可用。第 27.2.3 节中指定的检查限制了可以加载的选择器值。特别是,CS 和 TR 永远不会加载零,因此永远不会不可用。仅在支持 Intel 64 架构的处理器上并且仅当 VM Exits到 64 位模式时(64 位模式允许使用标记为不可用的段),SS 才可以加载为零。

-

基地址设置如下:

-

CS。清零。

-

SS、DS 和 ES。如果该段不可用,则未定义;否则清零

-

FS 和 GS。如果段不可用且 VM Exits不是 64 位模式,则未定义(但在支持 Intel 64 架构的处理器上,规范);否则,从基地址字段加载。

如果处理器支持 Intel 64 架构并且处理器支持 N < 64 线性地址位,则 63:N 位中的每一位都设置为位 N–1.1 的值。为 FS 和 GS 基地址加载的值也显示在FS.base 和 GS.base MSR。

-

TR。从host状态区域加载。如果处理器支持 Intel 64 架构并且处理器支持 N < 64 个线性地址位,则每个位 63:N 将设置为位 N–1 的值。

-

-

段限制设置如下:

- CS。设置为 FFFFFFFFH(对应于描述符限制 FFFFFH 和 G 位设置 1)。

- SS、DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,设置为 FFFFFFFFH。

- TR。设置为00000067H

-

类型字段和S位设置如下:

- CS。 Type 设置为 11,S 设置为 1(执行/读取、访问、不合格代码段)

- SS、DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,type 设置为 3,S 设置为 1(读/写、访问、扩展数据段)。

- TR。 Type 设置为 11,S 设置为 0(繁忙的 32 位任务状态段)

-

DPL 设置如下:

- CS、SS 和 TR。设置为 0。VM Exits完成后,当前权限级别 (CPL) 将为 0

- DS、ES、FS 和 GS。如果该段不可用,则未定义;否则设置为 0

-

P 位设置如下:

- CS、TR。设置为 1。

- SS、DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,设置为 1

-

在支持 Intel 64 架构的处理器上,CS.L 加载了“host地址空间大小”VM Exits控制的设置。因为该控件的值也被加载到 IA32_EFER.LMA(请参阅第 28.5.1 节),所以任何 VM Exits都不会进入兼容模式(这需要 IA32_EFER.LMA = 1 且 CS.L = 0)。

-

D B。

- CS。加载与“host地址空间大小”VM Exits控制设置相反的内容。例如,如果该控制为 0,表示 32 位客户机,则 CS.D/B 设置为 1。

- SS。设置为 1。

- DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,设置为 1。

- TR。设置为 0。

-

G。

- CS。设置为 1。

- SS、DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,设置为 1

- TR。设置为 0

-

CS。清零。

-

SS、DS 和 ES。如果该段不可用,则未定义;否则清零

-

FS 和 GS。如果段不可用且 VM Exits不是 64 位模式,则未定义(但在支持 Intel 64 架构的处理器上,规范);否则,从基地址字段加载。

如果处理器支持 Intel 64 架构并且处理器支持 N < 64 线性地址位,则 63:N 位中的每一位都设置为位 N–1.1 的值。为 FS 和 GS 基地址加载的值也显示在FS.base 和 GS.base MSR。

-

TR。从host状态区域加载。如果处理器支持 Intel 64 架构并且处理器支持 N < 64 个线性地址位,则每个位 63:N 将设置为位 N–1 的值。

- CS。设置为 FFFFFFFFH(对应于描述符限制 FFFFFH 和 G 位设置 1)。

- SS、DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,设置为 FFFFFFFFH。

- TR。设置为00000067H

- CS。 Type 设置为 11,S 设置为 1(执行/读取、访问、不合格代码段)

- SS、DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,type 设置为 3,S 设置为 1(读/写、访问、扩展数据段)。

- TR。 Type 设置为 11,S 设置为 0(繁忙的 32 位任务状态段)

- CS、SS 和 TR。设置为 0。VM Exits完成后,当前权限级别 (CPL) 将为 0

- DS、ES、FS 和 GS。如果该段不可用,则未定义;否则设置为 0

- CS、TR。设置为 1。

- SS、DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,设置为 1

- CS。加载与“host地址空间大小”VM Exits控制设置相反的内容。例如,如果该控制为 0,表示 32 位客户机,则 CS.D/B 设置为 1。

- SS。设置为 1。

- DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,设置为 1。

- TR。设置为 0。

- CS。设置为 1。

- SS、DS、ES、FS 和 GS。如果该段不可用,则未定义;否则,设置为 1

- TR。设置为 0

- VM退出后逻辑处理器始终处于活动状态

- 事件阻塞受到如下影响:

- VM Exits后,STI 或 MOV SS 不会阻塞。

- 由不可屏蔽中断 (NMI) 直接引起的 VM Exits会导致 NMI 阻塞(参见表 25-3)。其他 VM Exits不会影响 NMI 的阻止。 (有关 NMI 间接导致 VM Exits的情况,请参阅第 28.1 节。)

- VM Exits后不存在待处理的调试异常。

- VM Exits后,STI 或 MOV SS 不会阻塞。

- 由不可屏蔽中断 (NMI) 直接引起的 VM Exits会导致 NMI 阻塞(参见表 25-3)。其他 VM Exits不会影响 NMI 的阻止。 (有关 NMI 间接导致 VM Exits的情况,请参阅第 28.1 节。)

- 如果“启用 VPID”VM 执行控制为 0,则逻辑处理器将使与 VPID 0000H 关联的线性映射和组合映射(对于所有 PCID)无效; VPID 0000H 的组合映射对于所有 EP4TA 值均无效(EP4TA 是 EPTP 的位 51:12 的值)。

- 如果“启用 VPID”VM 执行控制为 1,则 VM Exits不需要使任何guest 物理映射无效,也不需要使任何线性映射或组合映射无效。

- 位 31:0 的值为 C0000100H(IA32_FS_BASE MSR)或 C0000101H(IA32_GS_BASE MSR)。

- 位 31:8 的值为 000008H,这意味着当本地 APIC 处于 x2APIC 模式时,索引 MSR 允许访问 APIC 寄存器。

- 位 31:0 的值指示只能在系统管理模式 (SMM) 下写入的 MSR,并且 VM Exits不会以 SMM 结束。 (IA32_SMM_MONITOR_CTL是只能在SMM中写入的MSR。)

- 位 31:0 的值指示由于特定于模型的原因而无法在 VM 出口上加载的 MSR。处理器可能会阻止加载某些 MSR,即使它们通常可以由 WRMSR 写入。此类特定于模型的行为记录在《英特尔® 64 和 IA-32 架构软件开发人员手册》第 4 卷的第 2 章“特定于模型的寄存器 (MSR)”中。

- 位 63:32 不全为 0。

- 如果在 CPL = 0 的情况下通过 WRMSR 执行,尝试将位 127:64 写入由条目的位 31:0 索引的 MSR 将导致一般保护异常。

- 如果逻辑处理器处于 SMX 操作中,则会发生英特尔® TXT 关闭情况。使用的错误代码是 000DH,表示“VMX 中止”。请参阅英特尔® 可信执行技术测量启动环境编程指南。

- 如果逻辑处理器处于 SMX 操作之外,它会发出一个特殊的总线周期(以通知芯片组)并进入 VMX-abort 关闭状态。 RESET 是将逻辑处理器从 VMX 中止关闭状态唤醒的唯一事件。以下事件不会影响处于此状态的逻辑处理器:机器检查事件; INIT 信号;外部中断;不可屏蔽中断(NMI);初创企业 IPI (SIPI);和系统管理中断(SMI)。

-

处理机器检查事件就好像它发生在虚拟机退出之前一样:

- 如果 CR4.MCE = 0,逻辑处理器的操作取决于逻辑处理器是否处于 SMX 操作:1

- 如果逻辑处理器处于 SMX 操作中,则会发生英特尔® TXT 关闭情况。使用的错误代码是000CH,表示“不可恢复的机器检查状况”。

- 如果逻辑处理器不在 SMX 操作范围内,则它会进入关闭状态

- 如果 CR4.MCE = 1,则会生成机器检查异常 (#MC):

- 如果异常位图的位 18 (#MC) 为 0,则异常通过客户 IDT 传递。

- 如果异常位图的位 18 为 1,则异常会导致 VM Exits。

- 如果 CR4.MCE = 0,逻辑处理器的操作取决于逻辑处理器是否处于 SMX 操作:1

-

机器检查事件在 VM Exits完成后处理:

- 如果 VM Exits以 CR4.MCE = 0 结束,则逻辑处理器的操作取决于逻辑处理器是否处于 SMX 操作中:

- 如果逻辑处理器处于 SMX 操作中,则会发生英特尔® TXT 关闭情况,并显示错误代码 000CH(不可恢复的机器检查情况)。

- 如果逻辑处理器不在 SMX 操作范围内,它将进入关闭状态。

- 如果 VM Exits以 CR4.MCE = 1 结束,则通过host IDT 传递机器检查异常 (#MC)

- 如果 VM Exits以 CR4.MCE = 0 结束,则逻辑处理器的操作取决于逻辑处理器是否处于 SMX 操作中:

-

生成 VMX 中止(请参阅第 28.7 节)。逻辑处理器会像通常那样阻止事件

VMX 中止。 VMX 中止指示器为 5,表示“VM Exits期间的机器检查事件”。

- 如果 CR4.MCE = 0,逻辑处理器的操作取决于逻辑处理器是否处于 SMX 操作:1

- 如果逻辑处理器处于 SMX 操作中,则会发生英特尔® TXT 关闭情况。使用的错误代码是000CH,表示“不可恢复的机器检查状况”。

- 如果逻辑处理器不在 SMX 操作范围内,则它会进入关闭状态

- 如果 CR4.MCE = 1,则会生成机器检查异常 (#MC):

- 如果异常位图的位 18 (#MC) 为 0,则异常通过客户 IDT 传递。

- 如果异常位图的位 18 为 1,则异常会导致 VM Exits。

- 如果逻辑处理器处于 SMX 操作中,则会发生英特尔® TXT 关闭情况。使用的错误代码是000CH,表示“不可恢复的机器检查状况”。

- 如果逻辑处理器不在 SMX 操作范围内,则它会进入关闭状态

- 如果异常位图的位 18 (#MC) 为 0,则异常通过客户 IDT 传递。

- 如果异常位图的位 18 为 1,则异常会导致 VM Exits。

- 如果 VM Exits以 CR4.MCE = 0 结束,则逻辑处理器的操作取决于逻辑处理器是否处于 SMX 操作中:

- 如果逻辑处理器处于 SMX 操作中,则会发生英特尔® TXT 关闭情况,并显示错误代码 000CH(不可恢复的机器检查情况)。

- 如果逻辑处理器不在 SMX 操作范围内,它将进入关闭状态。

- 如果 VM Exits以 CR4.MCE = 1 结束,则通过host IDT 传递机器检查异常 (#MC)

- 如果逻辑处理器处于 SMX 操作中,则会发生英特尔® TXT 关闭情况,并显示错误代码 000CH(不可恢复的机器检查情况)。

- 如果逻辑处理器不在 SMX 操作范围内,它将进入关闭状态。

- 关于VM退出原因的信息被记录在VM退出信息字段中,并且VM进入控制字段被修改,如第28.2节中所述。

- 处理器状态保存在客户状态区域(第 28.3 节)

- MSR 可以保存在 VM Exits MSR 存储区域中(第 28.4 节)。对于激活 SMI 和 SMM 的双监视器处理的 SMM VM Exits,不执行此步骤。

- 以下可以以任何顺序并行执行(第 28.5 节):

- 处理器状态的加载部分基于host状态区域和一些虚拟机退出控制。对于激活 SMI 和 SMM 的双监视器处理的 SMM VM Exits,不执行此步骤。有关此类 VM 出口如何加载处理器状态的信息,请参阅第 32.15.6 节。

- 地址范围监控已清除。

- MSR 可以从 VM Exits MSR 加载区域加载(第 28.6 节)。对于激活 SMI 和 SMM 的双监视器处理的 SMM VM Exits,不执行此步骤。

-

一般来说,该字段的格式与DR6的格式一致。然而,DR6 清零位 11 以指示检测到总线锁定,而该字段设置该位以指示该情况。

-

一般来说,该字段的格式与DR6的格式一致。然而,DR6 清除位 16 以指示与 RTM 相关的异常,而该字段设置该位以指示该情况。

-

对于页错误异常,退出限定包含导致页错误的线性地址。在支持 Intel 64 架构的处理器上,如果逻辑处理器在 VM Exits之前未处于 64 位模式,则清除位 63:32。

如果页错误异常发生在飞地模式下的指令执行期间(而不是在传送飞地模式的事件期间),则退出资格的位 11:0 被清除。

-

对于启动 IPI (SIPI),退出资格包含位 7:0 中的 SIPI 向量信息。退出资格的位 63:8 被清除为 0。

-

对于任务切换,退出限定包含有关任务切换的详细信息,编码如表 28-2 所示。

-

对于 INVLPG,退出限定包含指令的线性地址操作数。

-

在支持 Intel 64 架构的处理器上,如果逻辑处理器在 VM Exits之前未处于 64 位模式,则清除位 63:32。

-

如果 INVLPG 源操作数指定不可用的段,则退出限定中指定的线性地址将与 INVLPG 在未发生 VM Exits时使用的线性地址相匹配。该地址没有在体系结构上定义,并且可能是特定于实现的。

-

-

对于 INVEPT、INVPCID、INVVPID、LGDT、LIDT、LLDT、LTR、SGDT、SIDT、SLDT、STR、VMCLEAR、VMPTRLD、VMPTRST、VMREAD、VMWRITE、VMXON、XRSTORS 和 XSAVES,退出限定接收指令位移的值字段,如有必要,该字段将符号扩展为 64 位(在不支持 Intel 64 架构的处理器上为 32 位)。如果指令没有位移(例如,有寄存器操作数),则将零存储到退出限定中。

在支持 Intel 64 架构的处理器上,RIP 相对寻址(仅在 64 位模式下使用)是一个例外。此类寻址使指令使用的地址是位移字段与引用后续指令的 RIP 值之和。在这种情况下,退出资格加载位移场和适当的 RIP 值的总和。

在所有情况下,该字段超出指令地址大小的位都是未定义的。例如,假设 VM Exits指令信息字段(参见第 25.9.4 节和第 28.2.5 节)中的地址大小字段报告 n 位地址大小。那么指令位移的位 63: n(在不支持 Intel 64 架构的处理器上为位 31: n)未定义。

-

对于控制寄存器访问,退出限定包含有关访问的信息,其格式如表 28-3 所示。

-

对于 MOV DR,退出限定包含有关指令的信息,其格式如表 28-4 所示。

-

对于 I/O 指令,退出限定包含有关指令的信息,其格式如表 28-5 所示。

-

对于 MWAIT,退出限定包含一个值,该值指示是否进行地址范围监控

硬件已武装。退出资格设置为 0(如果地址范围监控硬件未配备)或 1(如果地址范围监控硬件配备)。

-

WBINVD 和 WBNOINVD 使用相同的基本退出原因(请参阅附录 C)。对于 WBINVD,退出资格为 0,而对于 WBNOINVD,退出资格为 1。

-

对于由于对 APIC 访问页面的线性访问或guest 物理访问而导致的 APIC 访问 VM Exits(请参阅第 30.4 节),退出限定包含有关访问的信息,并具有表 28-6 中给出的格式。

-

如果对 APIC 访问页的访问发生在飞地模式下的指令执行期间(而不是在飞地模式发生事件的传送期间),则退出资格的位 11:0 被清除。

这样的 VM Exits将退出限定的位 15:12 设置为 0000b(指令执行期间读取数据)或 0001b(指令执行期间数据写入)将位 12(区分数据读取和数据写入)设置为存储在页错误错误代码的位 1(W/R)中的访问导致了页错误,而不是 APIC 访问 VM Exits。这意味着以下内容:

-

对于由 CLFLUSH 和 CLFLUSHOPT 指令引起的 APIC 访问 VM Exits,访问类型是“指令执行期间读取数据”。

-

对于由ENTER指令引起的APIC访问VM退出,访问类型是“指令执行期间的数据写入”。

-

对于由MASKMOVQ指令或MASKMOVDQU指令引起的APIC访问VM退出,访问类型是“指令执行期间的数据写入”。

-

对于由 MONITOR 指令引起的 APIC 访问 VM Exits,访问类型是“指令执行期间读取数据”。

-

对于由于访问 DS 保存区(BTS 或 PEBS)中的线性地址直接导致的 APIC 访问 VM Exits,访问类型为“用于监视的线性访问”。

-

对于因访问 DS 保存区域(例如,访问分页结构以转换线性地址)而执行的guest 物理访问而导致的 APIC 访问 VM Exits,访问类型为“用于监视或监视的guest 物理访问”痕迹。”

-

对于当“Intel PT 使用guest 物理地址”VM 执行控制为 1 时由跟踪地址预转换 (TAPT) 导致的 APIC 访问 VM Exits,访问类型为“用于监视或跟踪的guest 物理访问”。

当且仅当它将退出资格的位 15:12 设置为 0011b(事件传递期间的线性访问)或 1010b(guest 物理事件交付期间的访问)。

有关这些指令和 APIC 访问 VM 出口的进一步讨论,请参见第 30.4.4 节。

对于因物理访问 APIC 访问页面而导致的 APIC 访问 VM Exits(请参阅第 30.4.6 节),退出资格未定义。

-

对于 EPT 违规,退出资格包含有关导致 EPT 违规的访问的信息,并具有表 28-7 中给出的格式。

如该表中所述,退出资格的格式和含义取决于“EPT 的基于模式的执行控制”VM 执行控制的设置以及处理器是否支持针对 EPT 违规的高级 VM Exits信息。

由于执行读取-修改-写入操作而发生的 EPT 违规设置位 1(数据写入)。是否也设置位 0(数据读取)是特定于实现的,并且对于给定的实现,对于不同类型的读取-修改-写入操作可能有所不同。

位 12 报告“NMI 由于 IRET 解锁”;参见第 28.2.3 节。

位 16 被设置用于与指令执行异步且不是事件传递的一部分的某些访问。其中包括 Intel PT 的跟踪地址预translation (TAPT)(请参阅第 26.5.4 节)、与具有“EPT 友好”增强功能的处理器上的 PEBS 相关的访问(请参阅第 20.9.5 节)以及作为用户一部分的访问- 中断传送(参见第 7.4.2 节)。

-

对于作为 EOI 虚拟化的一部分引起的 VM Exits(第 30.1.4 节),退出资格的位 7:0 设置为由 EOI 虚拟化消除的虚拟中断的向量。位 7 以上的位被清除。

-

对于 APIC 写入 VM Exits(第 30.4.3.3 节),退出限定的位 11:0 设置为导致 VM Exits的写访问的页偏移量。1 位 11 以上的位被清除。

-

对于由于页面修改日志满事件(第 29.3.6 节)而导致的 VM Exits,退出资格的位 12 报告“由于 IRET 导致 NMI 解锁”(请参阅第 28.2.3 节)。如果在 TAPT、EPT 友好的 PEBS 或用户中断传送期间发生 VM Exits,则设置位 16。退出资格的所有其他位均未定义。

-

对于由于 SPP 相关事件(第 29.3.4 节)而导致的 VM Exits,退出资格的位 11 指示事件类型:0 指示 SPP 配置错误,1 指示 SPP 未命中。退出资格的位 12 报告“NMI 由于 IRET 解锁”(参见第 28.2.3 节)。如果在 TAPT EPT 友好的 PEBS 或用户中断传送期间发生 VM Exits,则设置位 16。退出资格的所有其他位均未定义。

-

如果“PASID 转换”VM 执行控制,则为 ENQCMD 和 ENQCMDS 指令的执行执行 PASID 转换(请参见第 26.5.8 节)。 PASID 转换可能会失败,从而导致 VM Exits。这样的VM退出保存在以下项目中指定的退出资格:

- 对于 ENQCMD,退出资格是 IA32_PASID[19:0]。

- 对于 ENQCMDS,退出限定包含指令源操作数的低 32 位(在 PASID 转换之前已从内存中读取)。

-

对于由于指令超时而导致的 VM Exits(第 26.2 节),位 0 指示(如果设置)虚拟机的上下文无效并且不应恢复 VM。退出资格的位 12 报告“NMI 由于 IRET 解锁”(参见第 28.2.3 节)。退出资格的所有其他位均未定义。

-

-

- 如果启用了 EPT 的已访问标志和脏标志,则处理器对guest 分页结构条目的访问将被视为与 EPT 违规有关的写入(请参阅第 29.3.3.2 节)。如果此类访问导致 EPT 违规,则处理器将设置退出资格的位 0 和位 1。

- 如果任何 EPT 分页结构条目用于转换访问的guest 物理地址,则位 5:3 被清除为 0

- 软件可以通过咨询 VMX 功能 MSR IA32_VMX_EPT_VPID_CAP 来确定是否支持 EPT 违规的高级 VM Exits信息(请参阅附录 A.10)。

- 保存guest MSR 失败(请参阅第 28.4 节)。

- host对页目录指针表条目(PDPTE)的检查失败(参见第 28.5.4 节)。

- 当前 VMCS 已损坏(通过写入相应的 VMCS 区域),导致逻辑处理器无法正确完成 VM Exits。

- 加载host MSR 失败(请参阅第 28.6 节)。

- VM Exits期间发生机器检查事件(请参阅第 28.8 节)。

- 在 VM Exits之前,逻辑处理器处于 IA-32e 模式,并且“host地址空间大小”VM Exits控制为 0(参见第 28.5 节)。

[注意]传递专业知识、拓宽行业人脉——看雪讲师团队等你加入!