-

-

[原创] 修复 Miasm 源码缺失armt TEQ , CMN (register) of T2, TST (register) of T2 指令

-

发表于: 2019-9-21 19:36 5688

-

[原创] 修复 Miasm 源码缺失armt TEQ , CMN (register) of T2, TST (register) of T2 指令

2019-9-21 19:36

5688

【问题起源】

实情如,处理以下指令:

91 EA 03 0F TEQ.W R1, R3 92 EA 00 0F TEQ.W R2, R0 90 EA 02 0F TEQ.W R0, R2 93 EA 02 0F TEQ.W R3, R2 93 EA 01 0F TEQ.W R3, R1

会出现类似下述错误警告:

WARNING: cannot disasm (guess) at 39B0 WARNING: cannot disasm at 39B0

【问题修复】

经源码审查,问题源于miasm/arch/arm/arch.py的Thumb模式缺失了TEQ指令的定义(ARM模式正常),同时发现的,Thumb也缺失CMN和TST指令T2模型。

这里在

miasm/arch/arm/arch.py

文件末端添加以下代码对缺失Thumb 指令进行补充定义。

armtop("TEQ", [bs('11110'), imm12_1, bs('001001'), rn, bs('0'), imm12_3, bs('1111'), imm12_8], [rn, imm12_8])

armtop("TEQ", [bs('11101010100'), bs('1'), rn, bs('0'), imm5_3, bs('1111'), imm5_2, imm_stype, rm_sh], [rn, rm_sh] )

armtop("CMN", [bs('11101011000'), bs('1'), rn, bs('0'), imm5_3, bs('1111'), imm5_2, imm_stype, rm_sh], [rn, rm_sh] )

armtop("TST", [bs('11101010000'), bs('1'), rn, bs('0'), imm5_3, bs('1111'), imm5_2, imm_stype, rm_sh], [rn, rm_sh] )【修复原理】

上述指令定义原型来自ARM官方文件 DDI0406C_d_armv7ar_arm.pdf ,参考附件。

TEQ (immediate)

#T1 ARMv6T2, ARMv7

TEQ<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 0 1 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn);

(imm32, carry) = ThumbExpandImm_C(i:imm3:imm8, APSR.C);

if n IN {13,15} then UNPREDICTABLE;

TEQ(register)

#T1 ARMv6T2,ARMv7 Page.741

TEQ<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 1 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;

CMN (register)

#T2 ARMv6T2, ARMv7

CMN<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 1 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n == 15 || m IN {13,15} then UNPREDICTABLE;

TST (register)

#T2 ARMv6T2, ARMv7

TST<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;CMP,CMN,TEQ,TST 四种指令 ARM版(A*版)与Thumb 版(T*版)所有原型的定义如下。

miasm,mn_arm 主要对A1、A2、A3版本(A*版)指令定义,而mn_armt需要对T1、T2、T3版本(T*版)指令定义。

由此问题延伸的出的,在使用miasm过程中,mn_armt很可能缺失T2、T3版本指令的定义,也可能缺乏新版指令原型定义,这时需要我们自行补充。

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

CMP (immediate)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, #<imm8>

15 14 13 - 12 11 - 10 09 08 - 07 06 05 04 03 02 01 00

0 0 1 0 1 Rn imm8

n = UInt(Rn); imm32 = ZeroExtend(imm8, 32);

#T2 ARMv6T2, ARMv7

CMP<c>.W <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 1 1 0 1 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn); imm32 = ThumbExpandImm(i:imm3:imm8);

if n == 15 then UNPREDICTABLE;

#A! ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 1 0 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn); imm32 = ARMExpandImm(imm12);

CMP (register)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm> #<Rn> and <Rm> both from R0-R7

15 14 13 12 11 10 - 09 08 07 06 - 05 04 03 - 02 01 00

0 1 0 0 0 0 1 0 1 0 Rm Rn

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

#T2 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm> #<Rn> and <Rm> not both from R0-R7

15 14 13 12 11 10 - 09 08 - 07 - 06 05 04 03 - 02 01 00

0 1 0 0 0 1 0 1 N Rm Rn

n = UInt(N:Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

if n < 8 && m < 8 then UNPREDICTABLE;

if n == 15 || m == 15 then UNPREDICTABLE;

#T3 ARMv6T2, ARMv7

CMP<c>.W <Rn>, <Rm> {, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 1 1 0 1 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n == 15 || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 0 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

CMP (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 0 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

CMN (immediate)

#T1 ARMv6T2, ARMv7

CMN<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 1 0 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn); imm32 = ThumbExpandImm(i:imm3:imm8);

if n == 15 then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 1 1 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn); imm32 = ARMExpandImm(imm12);

CMN (register)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, <Rm>

15 14 13 12 11 10 - 09 08 07 06 - 05 04 03 - 02 01 00

0 1 0 0 0 0 1 0 1 1 Rm Rn

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

#T2 ARMv6T2, ARMv7

CMN<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 1 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n == 15 || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 1 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

CMN (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 1 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

TEQ (immediate)

#T1 ARMv6T2, ARMv7

TEQ<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 0 1 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn);

(imm32, carry) = ThumbExpandImm_C(i:imm3:imm8, APSR.C);

if n IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TEQ<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 0 1 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn);

(imm32, carry) = ARMExpandImm_C(imm12, APSR.C);

TEQ(register)

#T1 ARMv6T2,ARMv7 Page.741

TEQ<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 1 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TEQ<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 1 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

TEQ (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TEQ<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 1 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

TST (immediate)

#T1 ARMv6T2, ARMv7 //armtop("tst", [bs('11110'), imm12_1, bs('000001'), rn, bs('0'), imm12_3, bs('1111'), imm12_8], [rn, imm12_8])

TST<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 0 0 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn);

(imm32, carry) = ThumbExpandImm_C(i:imm3:imm8, APSR.C);

if n IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 0 0 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn);

(imm32, carry) = ARMExpandImm_C(imm12, APSR.C);

TST (register)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, <Rm>

15 14 13 12 11 10 - 09 08 07 06 - 05 04 03 - 02 01 00

0 1 0 0 0 0 1 0 0 0 Rm Rn

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

#T2 ARMv6T2, ARMv7

TST<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 0 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

TST (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 0 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;【如何比对哪些指令原型已经细化定义,哪些没有?】

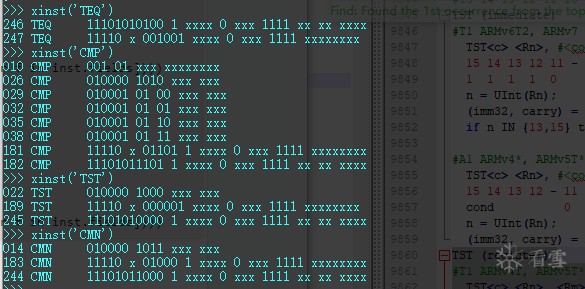

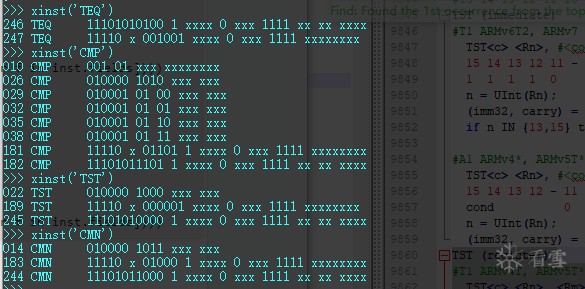

通过如下代码,我们可以查阅miasm特定芯片处理器架构已经定义的所有指令原型或特定指令原型,

通过比对最新版芯片指令集的编码规范文件,我们就可以知道已经定义了哪些、缺失了哪些。

from miasm2.arch.arm.arch import mn_armt

insts=mn_armt.all_mn

for inst in insts:

print("{:03} {} {}".format(inst.num,inst.name.ljust(7),' '.join([f.strbits if f.strbits else 'x'*f.l for f in inst.fields])))

def xinst(n='TEQ'):

n = n.upper()

for inst in insts:

if inst.name.startswith(n)

print("{:03} {} {}".format(inst.num,inst.name.ljust(7),' '.join([f.strbits if f.strbits else 'x'*f.l for f in inst.fields])))以下是修复后的相关指令的所有T*版原型定义。

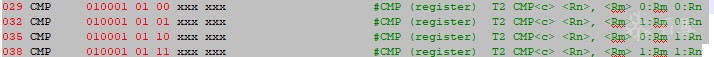

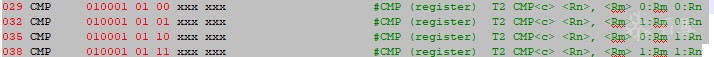

在审核miasm指令定义时,应当注意官方原型的区别,上图CMP的29,32,25,38号CMP指令原型。

实际对应CMP (register) T2版,由于miasm将部分CMP指令原型与部分mov,add,sub指令归类,所以派生了四种原型。

miasm 关于 mn_armt 的所有指令原型(我们从中,如先后顺序,也可得知源码是如何归类定义相应指令集)

91 EA 03 0F TEQ.W R1, R3 92 EA 00 0F TEQ.W R2, R0 90 EA 02 0F TEQ.W R0, R2 93 EA 02 0F TEQ.W R3, R2 93 EA 01 0F TEQ.W R3, R1

会出现类似下述错误警告:

91 EA 03 0F TEQ.W R1, R3 92 EA 00 0F TEQ.W R2, R0 90 EA 02 0F TEQ.W R0, R2 93 EA 02 0F TEQ.W R3, R2 93 EA 01 0F TEQ.W R3, R1

会出现类似下述错误警告:

WARNING: cannot disasm (guess) at 39B0 WARNING: cannot disasm at 39B0

【问题修复】

WARNING: cannot disasm (guess) at 39B0 WARNING: cannot disasm at 39B0

【问题修复】

经源码审查,问题源于miasm/arch/arm/arch.py的Thumb模式缺失了TEQ指令的定义(ARM模式正常),同时发现的,Thumb也缺失CMN和TST指令T2模型。

这里在

miasm/arch/arm/arch.py

文件末端添加以下代码对缺失Thumb 指令进行补充定义。

armtop("TEQ", [bs('11110'), imm12_1, bs('001001'), rn, bs('0'), imm12_3, bs('1111'), imm12_8], [rn, imm12_8])

armtop("TEQ", [bs('11101010100'), bs('1'), rn, bs('0'), imm5_3, bs('1111'), imm5_2, imm_stype, rm_sh], [rn, rm_sh] )

armtop("CMN", [bs('11101011000'), bs('1'), rn, bs('0'), imm5_3, bs('1111'), imm5_2, imm_stype, rm_sh], [rn, rm_sh] )

armtop("TST", [bs('11101010000'), bs('1'), rn, bs('0'), imm5_3, bs('1111'), imm5_2, imm_stype, rm_sh], [rn, rm_sh] )armtop("TEQ", [bs('11110'), imm12_1, bs('001001'), rn, bs('0'), imm12_3, bs('1111'), imm12_8], [rn, imm12_8])

armtop("TEQ", [bs('11101010100'), bs('1'), rn, bs('0'), imm5_3, bs('1111'), imm5_2, imm_stype, rm_sh], [rn, rm_sh] )

armtop("CMN", [bs('11101011000'), bs('1'), rn, bs('0'), imm5_3, bs('1111'), imm5_2, imm_stype, rm_sh], [rn, rm_sh] )

armtop("TST", [bs('11101010000'), bs('1'), rn, bs('0'), imm5_3, bs('1111'), imm5_2, imm_stype, rm_sh], [rn, rm_sh] )【修复原理】

上述指令定义原型来自ARM官方文件 DDI0406C_d_armv7ar_arm.pdf ,参考附件。

TEQ (immediate)

#T1 ARMv6T2, ARMv7

TEQ<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 0 1 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn);

(imm32, carry) = ThumbExpandImm_C(i:imm3:imm8, APSR.C);

if n IN {13,15} then UNPREDICTABLE;

TEQ(register)

#T1 ARMv6T2,ARMv7 Page.741

TEQ<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 1 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;

CMN (register)

#T2 ARMv6T2, ARMv7

CMN<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 1 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n == 15 || m IN {13,15} then UNPREDICTABLE;

TST (register)

#T2 ARMv6T2, ARMv7

TST<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;TEQ (immediate)

#T1 ARMv6T2, ARMv7

TEQ<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 0 1 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn);

(imm32, carry) = ThumbExpandImm_C(i:imm3:imm8, APSR.C);

if n IN {13,15} then UNPREDICTABLE;

TEQ(register)

#T1 ARMv6T2,ARMv7 Page.741

TEQ<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 1 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;

CMN (register)

#T2 ARMv6T2, ARMv7

CMN<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 1 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n == 15 || m IN {13,15} then UNPREDICTABLE;

TST (register)

#T2 ARMv6T2, ARMv7

TST<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;CMP,CMN,TEQ,TST 四种指令 ARM版(A*版)与Thumb 版(T*版)所有原型的定义如下。

miasm,mn_arm 主要对A1、A2、A3版本(A*版)指令定义,而mn_armt需要对T1、T2、T3版本(T*版)指令定义。

由此问题延伸的出的,在使用miasm过程中,mn_armt很可能缺失T2、T3版本指令的定义,也可能缺乏新版指令原型定义,这时需要我们自行补充。

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

CMP (immediate)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, #<imm8>

15 14 13 - 12 11 - 10 09 08 - 07 06 05 04 03 02 01 00

0 0 1 0 1 Rn imm8

n = UInt(Rn); imm32 = ZeroExtend(imm8, 32);

#T2 ARMv6T2, ARMv7

CMP<c>.W <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 1 1 0 1 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn); imm32 = ThumbExpandImm(i:imm3:imm8);

if n == 15 then UNPREDICTABLE;

#A! ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 1 0 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn); imm32 = ARMExpandImm(imm12);

CMP (register)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm> #<Rn> and <Rm> both from R0-R7

15 14 13 12 11 10 - 09 08 07 06 - 05 04 03 - 02 01 00

0 1 0 0 0 0 1 0 1 0 Rm Rn

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

#T2 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm> #<Rn> and <Rm> not both from R0-R7

15 14 13 12 11 10 - 09 08 - 07 - 06 05 04 03 - 02 01 00

0 1 0 0 0 1 0 1 N Rm Rn

n = UInt(N:Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

if n < 8 && m < 8 then UNPREDICTABLE;

if n == 15 || m == 15 then UNPREDICTABLE;

#T3 ARMv6T2, ARMv7

CMP<c>.W <Rn>, <Rm> {, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 1 1 0 1 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n == 15 || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 0 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

CMP (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 0 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

CMN (immediate)

#T1 ARMv6T2, ARMv7

CMN<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 1 0 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn); imm32 = ThumbExpandImm(i:imm3:imm8);

if n == 15 then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 1 1 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn); imm32 = ARMExpandImm(imm12);

CMN (register)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, <Rm>

15 14 13 12 11 10 - 09 08 07 06 - 05 04 03 - 02 01 00

0 1 0 0 0 0 1 0 1 1 Rm Rn

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

#T2 ARMv6T2, ARMv7

CMN<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 1 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n == 15 || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 1 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

CMN (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 1 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

TEQ (immediate)

#T1 ARMv6T2, ARMv7

TEQ<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 0 1 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn);

(imm32, carry) = ThumbExpandImm_C(i:imm3:imm8, APSR.C);

if n IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TEQ<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 0 1 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn);

(imm32, carry) = ARMExpandImm_C(imm12, APSR.C);

TEQ(register)

#T1 ARMv6T2,ARMv7 Page.741

TEQ<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 1 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TEQ<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 1 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

TEQ (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TEQ<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 1 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

TST (immediate)

#T1 ARMv6T2, ARMv7 //armtop("tst", [bs('11110'), imm12_1, bs('000001'), rn, bs('0'), imm12_3, bs('1111'), imm12_8], [rn, imm12_8])

TST<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 0 0 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn);

(imm32, carry) = ThumbExpandImm_C(i:imm3:imm8, APSR.C);

if n IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 0 0 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn);

(imm32, carry) = ARMExpandImm_C(imm12, APSR.C);

TST (register)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, <Rm>

15 14 13 12 11 10 - 09 08 07 06 - 05 04 03 - 02 01 00

0 1 0 0 0 0 1 0 0 0 Rm Rn

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

#T2 ARMv6T2, ARMv7

TST<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 0 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

TST (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 0 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

CMP (immediate)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, #<imm8>

15 14 13 - 12 11 - 10 09 08 - 07 06 05 04 03 02 01 00

0 0 1 0 1 Rn imm8

n = UInt(Rn); imm32 = ZeroExtend(imm8, 32);

#T2 ARMv6T2, ARMv7

CMP<c>.W <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 1 1 0 1 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn); imm32 = ThumbExpandImm(i:imm3:imm8);

if n == 15 then UNPREDICTABLE;

#A! ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 1 0 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn); imm32 = ARMExpandImm(imm12);

CMP (register)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm> #<Rn> and <Rm> both from R0-R7

15 14 13 12 11 10 - 09 08 07 06 - 05 04 03 - 02 01 00

0 1 0 0 0 0 1 0 1 0 Rm Rn

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

#T2 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm> #<Rn> and <Rm> not both from R0-R7

15 14 13 12 11 10 - 09 08 - 07 - 06 05 04 03 - 02 01 00

0 1 0 0 0 1 0 1 N Rm Rn

n = UInt(N:Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

if n < 8 && m < 8 then UNPREDICTABLE;

if n == 15 || m == 15 then UNPREDICTABLE;

#T3 ARMv6T2, ARMv7

CMP<c>.W <Rn>, <Rm> {, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 1 1 0 1 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n == 15 || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 0 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

CMP (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMP<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 0 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

CMN (immediate)

#T1 ARMv6T2, ARMv7

CMN<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 1 0 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn); imm32 = ThumbExpandImm(i:imm3:imm8);

if n == 15 then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 1 1 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn); imm32 = ARMExpandImm(imm12);

CMN (register)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, <Rm>

15 14 13 12 11 10 - 09 08 07 06 - 05 04 03 - 02 01 00

0 1 0 0 0 0 1 0 1 1 Rm Rn

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

#T2 ARMv6T2, ARMv7

CMN<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 1 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n == 15 || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 1 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

CMN (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

CMN<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 1 1 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

TEQ (immediate)

#T1 ARMv6T2, ARMv7

TEQ<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 0 1 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn);

(imm32, carry) = ThumbExpandImm_C(i:imm3:imm8, APSR.C);

if n IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TEQ<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 0 1 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn);

(imm32, carry) = ARMExpandImm_C(imm12, APSR.C);

TEQ(register)

#T1 ARMv6T2,ARMv7 Page.741

TEQ<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 1 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TEQ<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 1 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

TEQ (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TEQ<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 1 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;

#15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 -- 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

TST (immediate)

#T1 ARMv6T2, ARMv7 //armtop("tst", [bs('11110'), imm12_1, bs('000001'), rn, bs('0'), imm12_3, bs('1111'), imm12_8], [rn, imm12_8])

TST<c> <Rn>, #<const>

15 14 13 12 11 - 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 05 04 03 02 01 00

1 1 1 1 0 i 0 0 0 0 0 1 Rn 0 imm3 1 1 1 1 imm8

n = UInt(Rn);

(imm32, carry) = ThumbExpandImm_C(i:imm3:imm8, APSR.C);

if n IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, #<const>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 06 05 04 03 02 01 00

cond 0 0 1 1 0 0 0 1 Rn (0)(0)(0)(0) imm12

n = UInt(Rn);

(imm32, carry) = ARMExpandImm_C(imm12, APSR.C);

TST (register)

#T1 ARMv4T, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, <Rm>

15 14 13 12 11 10 - 09 08 07 06 - 05 04 03 - 02 01 00

0 1 0 0 0 0 1 0 0 0 Rm Rn

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = (SRType_LSL, 0);

#T2 ARMv6T2, ARMv7

TST<c>.W <Rn>, <Rm>{, <shift>}

15 14 13 12 11 - 10 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 - 14 13 12 - 11 10 09 08 - 07 06 - 05 04 - 03 02 01 00

1 1 1 0 1 0 1 0 0 0 0 1 Rn (0) imm3 1 1 1 1 imm2 type Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm3:imm2);

if n IN {13,15} || m IN {13,15} then UNPREDICTABLE;

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, <Rm>{, <shift>}

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 0 1 Rn (0)(0)(0)(0) imm5 type 0 Rm

n = UInt(Rn); m = UInt(Rm);

(shift_t, shift_n) = DecodeImmShift(type, imm5);

TST (register-shifted register)

#A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7

TST<c> <Rn>, <Rm>, <type> <Rs>

15 14 13 12 - 11 10 - 09 - 08 07 06 05 - 04 - 03 02 01 00 -- 15 14 13 12 - 11 10 09 08 - 07 - 06 05 - 04 - 03 02 01 00

cond 0 0 0 1 0 0 0 1 Rn (0)(0)(0)(0) Rs 0 type 1 Rm

n = UInt(Rn); m = UInt(Rm); s = UInt(Rs);

shift_t = DecodeRegShift(type);

if n == 15 || m == 15 || s == 15 then UNPREDICTABLE;[培训]内核驱动高级班,冲击BAT一流互联网大厂工作,每周日13:00-18:00直播授课

最后于 2019-9-22 16:39

被HHHso编辑

,原因:

赞赏

他的文章

- [原创] KCTF 2022 Win. 第六题 约束与伪随机 6745

- [原创] KCTF 2021 Win. 第二题 排排坐 21174

- [原创] KCTF 2021 Win. 第一题 算力与攻击模式 4118

- 鸿蒙通识 26029

- [原创] KCTF 2021 Spr. 第二题 未选择的路 9249

谁下载

谁下载

谁下载

赞赏

雪币:

留言: