|

|

[已结束][PEDIY.华章 Crackme 竞赛 2009] [第四回] –CRC

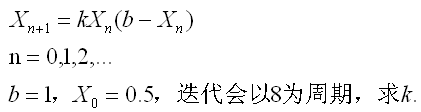

X(n+1)=kXn(1-Xn),即Xn只依赖于X(n-1). 若X(n+8)=Xn,则Xn必是8为周期。 Xn是以2为周期,则X(n+2)=X(n+2*2)=X(n+3*2)=X(n+4*2)=X(n+8)。 所以若不是严格以8为周期,可求X(n+2)=Xn,即可求得k。 如果它严格以8为周期,且存在有理数解, 则可通过划分k的区间后逐步求X(n+8)=X(n)。 |

|

|

[已结束][PEDIY.华章 Crackme 竞赛 2009] [第四回] –CRC

[QUOTE=海风月影;684834]谁会解这个,教教我。。。  [/QUOTE] [/QUOTE]它等价于求一元多次方程的解, 次数太高只能求它的近似解 k=3.23606797745时, X8-0.5=7.2658103641441418237206038342213e-14 k=2.500000000000000-->X8-X0=0.099791326874127 k=3.250000000000000-->X8-X0=-0.004734795096228 k=2.875000000000000-->X8-X0=0.126568694727795 k=3.062500000000000-->X8-X0=0.071996142849137 k=3.156250000000000-->X8-X0=0.030549039477106 k=3.203125000000000-->X8-X0=0.011862185062102 k=3.226562500000000-->X8-X0=0.003322345296137 k=3.238281250000000-->X8-X0=-0.000762638944560 k=3.232421875000000-->X8-X0=0.001265264887133 k=3.235351562500000-->X8-X0=0.000247728995916 k=3.236816406250000-->X8-X0=-0.000258343219337 k=3.236083984375000-->X8-X0=-0.000005530132844 k=3.235717773437500-->X8-X0=0.000121043555426 k=3.235900878906250-->X8-X0=0.000057742757402 k=3.235992431640625-->X8-X0=0.000026102825696 k=3.236038208007813-->X8-X0=0.000010285475016 k=3.236061096191406-->X8-X0=0.000002377453263 k=3.236072540283203-->X8-X0=-0.000001576394242 k=3.236066818237305-->X8-X0=0.000000400515897 k=3.236069679260254-->X8-X0=-0.000000587942576 k=3.236068248748779-->X8-X0=-0.000000093714190 k=3.236067533493042-->X8-X0=0.000000153400641 k=3.236067891120911-->X8-X0=0.000000029843172 k=3.236068069934845-->X8-X0=-0.000000031935523 k=3.236067980527878-->X8-X0=-0.000000001046178 k=3.236067935824394-->X8-X0=0.000000014398496 k=3.236067958176136-->X8-X0=0.000000006676158 k=3.236067969352007-->X8-X0=0.000000002814990 k=3.236067974939942-->X8-X0=0.000000000884405 k=3.236067977733910-->X8-X0=-0.000000000080887 k=3.236067976336926-->X8-X0=0.000000000401759 k=3.236067977035418-->X8-X0=0.000000000160436 k=3.236067977384664-->X8-X0=0.000000000039775 k=3.236067977559287-->X8-X0=-0.000000000020556 k=3.236067977471976-->X8-X0=0.000000000009610 k=3.236067977515631-->X8-X0=-0.000000000005473 k=3.236067977493804-->X8-X0=0.000000000002068 k=3.236067977504717-->X8-X0=-0.000000000001702 k=3.236067977499261-->X8-X0=0.000000000000183 k=3.236067977501989-->X8-X0=-0.000000000000760 k=3.236067977500625-->X8-X0=-0.000000000000288 k=3.236067977499943-->X8-X0=-0.000000000000053 k=3.236067977499602-->X8-X0=0.000000000000065 k=3.236067977499772-->X8-X0=0.000000000000006 k=3.236067977499857-->X8-X0=-0.000000000000023 k=3.236067977499815-->X8-X0=-0.000000000000009 k=3.236067977499793-->X8-X0=-0.000000000000001 k=3.236067977499783-->X8-X0=0.000000000000002 k=3.236067977499788-->X8-X0=0.000000000000001 k=3.236067977499791-->X8-X0=-0.000000000000000 k=3.236067977499789-->X8-X0=0.000000000000000 |

|

|

[推荐]Cache知识汇总

Reducing branch mispredicts with branch hint General-purpose processors have typically addressed branch prediction by supporting hardware look-asides with branch history tables (BHT), branch target address caches (BTAC), or branch target instruction caches (BTIC). The SPU addresses branch prediction through a set of hint for branch (HBR) instructions that facilitate efficient branch processing by allowing programs to avoid the penalty of taken branches. If a branch hint is provided, software speculates that the instruction branches to the target path. If a hint is not provided, software speculates that the instruction does not branch to a new location (that is, it stays inline). If speculation is incorrect, the speculated branch is flushed and refetched. It is possible to sequence multiple hints in advance of multiple branches. As with all programmer-provided hints, care must be exercised when using branch hints because, if the information provided is incorrect, performance might degrade. Branch-hint instructions can provide three kinds of advance knowledge about future branches: Address of the branch target (that is, where will the branch take the flow of control) Address of the actual branch instruction (known as the hint-trigger address ) Prefetch schedule (when to initiate prefetching instructions at the branch target) Branch-hint instructions load a branch-target buffer (BTB) in the SPU. When the BTB is loaded with a branch target, the hint-trigger address and branch address are also loaded into the BTB. After loading, the BTB monitors the instruction stream as it goes into the issue stage of the pipeline. When the address of the instruction going into issue matches the hint trigger address, the hint is triggered, and the SPU speculates to the target address in the hint buffer. Branch-hint instructions have no program-visible effects. They provide a hint to the SPE architecture about a future branch instruction, with the intention that the information be used to improve performance by prefetching the branch target. The SPE branch-hint instructions are shown in Table 1. There are immediate and indirect forms for this instruction class. The location of the branch is always specified by an immediate operand in the instruction. Table 1. Branch-Hint Instructions Instruction Description hbr s11, ra Hint for branch (r-form). Hint that the instruction addressed by the sum of the address of the current instruction and the signed extended, 11-bit value s11 will branch to the address contained in word element 0 of register ra. This form is used to hint function returns, pointer function calls, and other situations that give rise to indirect branches. hbra s11, s18 Hint for branch (a-form). Hint that the instruction addressed by the sum of the address of the current instruction and the signed extended, 11-bit value s11 will branch to the address specified by the sign extended, 18-bit value s18. hbrr s11, s18 Hint for branch relative. Hint that the instruction addressed by the sum of the address of the current instruction and the signed extended, 11-bit value s11 will branch to the address specified by the sum of the address of the current instruction and sign extended, 18-bit value s18. The following rules apply to the hint for branch (HBR) instructions: An HBR instruction should be placed at least 11 cycles followed by four instruction pairs before the branch instructions being hinted by the HBR instruction. In other words, an HBR instruction must be followed by at least 11 cycles of instructions, followed by eight instructions aligned on an even address boundary. More separation between the hint and branch improves the performance of applications on future SPU implementations. If an HBR instruction is placed too close to the branch, then a hint stall will result. This results in the branch instruction stalling until the timing requirement of the HBR instruction is satisfied. If an HBR instruction is placed closer to the hint-trigger address than four instruction pairs plus one cycle, then the hint stall does not occur and the HBR is not used. Only one HBR instruction can be active at a time. Issuing another HBR cancels the current one. An HBR instruction can be moved outside of a loop and will be effective on each loop iteration as long as another HBR instruction is not executed. The HBR instruction must be placed within 255 instructions of the branch instruction. The HBR instruction only affects performance. The HBR instructions can be used to support multiple strategies of branch prediction. These include: Static Branch Prediction — Prediction based upon branch type or displacement, and prediction based upon profiling or linguistic hints. Dynamic Branch Prediction — Software caching of branch-target addresses, and using control flow to record branching history. A common approach to generating static branch prediction is to use expert knowledge that is obtained either by feedback-directed optimization techniques or using linguistic hints supplied by the programmer. The document C/C++ Language Extensions for Cell Broadband Engine Architecture defines a mechanism for directing branch prediction. The __builtin_expect directive allows programmers to predict conditional program statements. The following example demonstrates how a programmer can predict that a conditional statement is false (a is not larger than b). if(__builtin_expect((a>b),0)) c += a; else d += 1; Not only can the __builtin_expect directive be used for static branch prediction, it can be used for dynamic branch prediction. |

|

|

[原创]使用RSA1024算法防止软件被Keygen

[QUOTE=boywhp;647793]傻啊!关键代码在狗的CPU跑 你截获通信数据有什么用?你那是早期的狗狗,只能起到一个验证的功能, 现在的狗内部都有CPU的,可以把代码写在狗里面,并且狗狗内部代码不可读出[/QUOTE] 当然有用,只不过狗的动算能力影响难度而已。 插值攻击、差分分析、双线性分析等等,只不过是破解代价的问题。 |

|

|

|

|

|

|

|

|

[求助]关于用Ms的CryptoAPI做RSA加密的疑问

“我就是想用私钥来加密,用公钥来解密。” 在CryptoAPI里无法实现,除非自己写函数。 并且也没有这样做的必要,因为“用私钥来加密,用公钥来解密” 这样等于没有加密。 |

|

|

[分享]A novel deniable authentication protocol

很强大,期待rockinuk放出结果 |

|

|

[求助]有关于winrar加解密步骤的资料吗?

http://bbs.pediy.com/showthread.php?t=62908 一个菜鸟关于winrar密码无法秒破的研究结果 by askyou |

|

|

|

|

|

[讨论]4字节数据的 加密

四个字节?分块太小了,算是置换。 设置换前为M,置换后为C,选择一个32位的随机数e(=3988292384), 及32位的素数P(=4294967291这个随便选,不过P越小C的碰撞越多)。 C=(M xor e)^3 mod P 这里选3是因为,(3,4294967291-1)=1, 即任意x<4294967291都是4294967291的3次剩余 00 00 00 01 A9 91 A5 33 00 00 00 02 F7 BE E2 12 00 00 00 04 4B 12 94 AD 00 00 00 08 CD 9E DD 5F 00 00 00 10 42 4B 02 B6 00 00 00 20 3D C8 9F 98 00 00 00 40 32 7A 80 8D 00 00 00 80 A8 83 43 9B 00 00 01 00 C5 84 CE D3 00 00 02 00 AA 2D FE 44 00 00 04 00 87 18 C0 5D 00 00 08 00 CE 37 BF 9A 00 00 10 00 65 AE EC 2F 2^32-P=4294967296-4294967291=5 所以仅只有5个C会碰撞 |

|

|

|

|

|

|

|

|

|

操作理由

RANk

{{ user_info.golds == '' ? 0 : user_info.golds }}

雪币

{{ experience }}

课程经验

{{ score }}

学习收益

{{study_duration_fmt}}

学习时长

基本信息

荣誉称号:

{{ honorary_title }}

勋章

兑换勋章

证书

证书查询 >

能力值